# A Novel Watchdog Timer for Real-Time Intensive Applications

Dr.R.SenthamilSelvan<sup>1</sup>, Dr.V.Mahalakshmi<sup>\*1</sup>, Dr.S.P.Vijayaragavan<sup>2</sup>, Dr.S.Arulselvi<sup>3</sup>, Dr.M.Jasmin<sup>3</sup> {senthamilselvan87@gmail.com<sup>1</sup>, mahachandru18@gmail.com<sup>\*1</sup>, vijayaragavansp@gmail.com<sup>2</sup>,

arulselvi2003@gmail.com<sup>3</sup>, rifriz@gmail.com<sup>3</sup>}

Associate Professor, Department of ECE, Chadalawada Ramanamma Engineering College, Tirupati, Andhra Pradesh, India.<sup>1</sup>, Associate Professor, Department of EEE, Prince Shri VenkateshwaraPadmavathy Engineering College, Chennai<sup>1\*</sup>, Associate Professor, Department of EEE, Bharath Institute of Higher Education and Research<sup>2</sup>

Abstract.Integrated systems utilized in security-critical applications require the very best accuracy. Externic monitoring watches are utilized in that structure naturally manages to get over failures associated with operating time. Most vacant exterior watch watches use extra circuits are regulate rest interlude and supply just partial appearance in terms of the performance. A document explains planning, style of enhanced arrangement of watchdog timer which utilized in security-demanding use. Various errors finding method are constructing watchdog, adding to its strength. A process is fairly common and not to observe procedure of a few relative method. This enables a planning is simply tailored to diverse use as dropping common price of a system. The efficiency of planned surveillance device to notice error is initially deliberate by examine the simulation outcome.

**Keywords:** FPGA, Watch Dog Timer (WDT), Hardware Description Language (HDL), Input and Output Interface, Verilog and VHDL.

## 1 Introduction

For applications where framework disappointment can cause injury, most extreme unwavering quality is required. Such frameworks must have adaptation to non-critical failure components that consider the sudden to guarantee satisfactory operational security. These frameworks ought to have the option to recuperate from a mishap without human help. This adaptation to internal failure components recognize when a deficiency happens, to cure the issue and breaking point framework personal time [1]. One approach to accomplish adaptation to non-critical failure is to execute framework repetition. The utilization of numerous duplicates of basic framework parts improves the dependability of the whole framework [2]. Notwithstanding, this improved unwavering quality of the framework is acquired gratitude to an expanded equipment and programming intricacy relying upon the sort of design utilized. By building up a shortcoming lenient framework, the guard dog is one of the most financially savvy strategies for identifying and dealing with blunders identified with uptime [3]. A guard dog clock (WDT) is an equipment subsystem that screens framework activity and makes certain move if a blunder is identified [4]. In the event that the WDT lapses, this is an auxiliary sign of an issue with the watched framework [5]. On the off chance that the processor can't reset the guard dog, the choice is made either to restart the framework, or to place it in a known state from which it recoup, which forestalls consecutive harm. Inward observing diminishes unpredictability and equipment costs; however it's anything but a strong arrangement. Hence, the system is associated with processor-clock, the guard dog can't screen the equipment for mistakes because of a quartz blunder [6]. At the point when the unwavering quality of an on-board framework is basic, outer guard dogs are unavoidable. The impediments of interior guard dogs and prompts substantially more vigorous & issue open minded framework structures[7]. A class of self-governing checking chips just offers fixed timespans, which makes them less broad. Different gadgets permit you to modify the lapse times utilizing extra outer circuits. While this technique is valuable, it builds the intricacy of the equipment and expands the general expense of the framework. The expanded expense and unpredictability of outer guard dogs can be figured out how somewhat by actualizing guard dog usefulness in an on location programmable entryway arrange (FPGA). Numerous cutting edge inserted frameworks in at least one of the organization's FPGA gadgets accomplish the ideal framework usefulness [8],[9]. Putting the checking clock on a FPGA can prompt a productive and hearty arrangement. The structure didn't offer a clock for the processor; despite what might be expected, a sufficiency look at was conveyed for specific factors and an essential check of the program progress. EL-Attar gives a successive checking clock shows pre-owned records to decide if a blunder had happened[10]. Be that as it may, barely any arrangement alternatives were offered and the mistake discovery capacities actualized were restricted. In [11], the creators talked about the nuts and bolts of a checking clock framework with different equipment parts in FPGA, yet kept the plan of observing basic. By actualizing field programmable gate array plan, a similar observing equipment can be associated with various processors and frameworks with just minor alterations to the related HDL code (Hardware Description Language) [8]. It likewise permits the incorporation of a few observing clocks for multicore designs. The proposed checking clock functions admirably for wellbeing basic on-board frameworks that utilization excess channels to improve framework unwavering quality. The plan of the WDT as a reusable IP center additionally addresses the out of date quality issues of the segments experienced by numerous.

# II. Design Of Watch Dog System

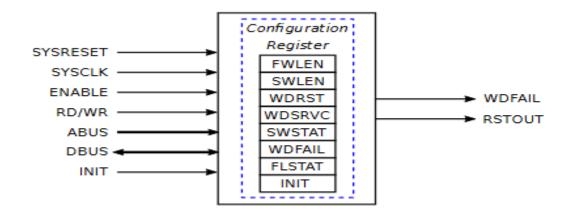

A valid watchdog should have the ability to identify all irregular programming modes and return the frame. It must be in good condition to allow the restoration of the equipment if all or some of the peripherals are cut [3]. The watchdog offered in this article works freely from the processor and uses a busy watch for its abilities. Engineering follows a use of window monitoring, in which window times are often designed by the merchandise during installation. A bomb banner is raised when the watchdog clock ends and after a hard and fast measurement of your time to raise the banner, a reset is activated. Time in the medium is often used by the goods to store important bearing data on an unpredictable medium. In frame, for example due to unlimited circles running code. The control contributions to the monitoring clock, ENABLE and RD / WR, develop a chain and limit contact with the disposition register. The ABUS and DBUS flags in an image show the transport of addresses and the transport of knowledge separately.

#### An Initial Setup of Timer

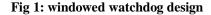

During startup or restart, the observer activates in a blinking state, which means that WDFAIL performance is high. It is the duty of the property to present and manage the guard dog. Figure 2 shows the waveform for resetting the guard dog and entering general activity. Therefore, in order to get the watchdog up and running, the watchdog reset field (WDRST) in the configuration record must first be changed from bottom to top. This cancels the WDFAIL header caused by the redesign of the watchdog in the management window and makes it working. Since the window window remains larger than the frame outline, another help window starts before this window expires. When the spotter has been successfully overhauled, the window will be restored. Regardless of how long the window counters work, the observer will not take a clock.

Fig 2: Initialization of Watchdog Timer and its working

## **III. Watchdog-Timer Implementation**

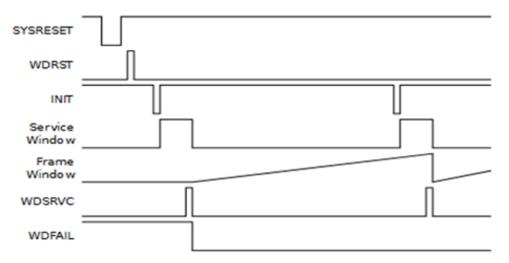

These segments capture the recognition of the surveillance fists presented in the FPGA. The high-level diagram of the monitoring equipment is illustrated in Figure 6. The structure is synchronized with the SYSCLK input released by the processor clock. plan. These attributes are usually selected after the force, in the location register - SWLEN for the application window and FWLEN for the navigation window - set to the correct bits. When choosing shades, the length zones of residential windows are naturally bolted; that is, sticking to these bits is disabled. In cases where the window lengths have to be changed again, there are 16 open records in the structure [10]. Therefore, when the length of the window changes, products must perform two-step registrations based on that registration with the information 0xAAAA and 0x5555. To successfully create most samples, you must create the following within 10  $\mu$ s, after which there is a period of 10  $\mu$ s to modify the length order fields of the goods. If these timings are not carefully controlled, staying tuned for these bits will be deficient. When a change from top to bottom of the INIT signal is detected, the administration window opens. The administration window uses a much slower specific time (SWCLK) than SYSCLK. Slow validation can reduce the number of comparators required, limiting the use of resources in FPGA. The management windows have a balanced SYSCLK up / down counter and a basic counter which runs in SWCLK. The counterweight counter balances the INIT input and therefore the subsequent growth eaves of SWCLK (Toffset). This is often necessary because the INIT flag cannot be determined simultaneously and SWCLK may appear each time during Tswclk time. The prediction of the balance is recorded then the main counter is started, at this time (SWLEN - 1) executed. When the master counter expires, the counter falls for a Tswclk-Toffset period [18]. This counting strategy takes into account a certain authority for the length of the window. The operational status of the administration window is also regularly updated in the monitor configuration log. When the monitoring is effectively modified, the counters in the management window stop quickly, then the integrated window starts. The container window also uses a specific slow clock (FWCLK) for its activities. It is a main counter with functions such as a balanced / decreasing counter and that of the administration window. The balance counter here finds the counterweight between the top of the application window and therefore the subsequent growth eaves of the FWCLK. The first counter displays the hours (FWLEN - 1) then the counter. In the next length of the help window, the window counters are reset when the guard management activity occurs before the window ends. A. Restart initialization and failure detection The graph in Figure 7 shows State Machine Limited (FSM) running for the causes of watchdog restart and failure detection. It has been confirmed that the performance of WDFAIL was disappointing for the watchdog during its operation [19]. The rising edge on the WDRST bit prepares the watchdog for installation. When the management window is open, the rising edge on the WDSRVC bit cancels the performance of WDFAIL and, consequently, the window counters start to run. In all cases, if the watchdog is incorrectly configured, the entire input process is deleted and the product must therefore repeat the entire method. The WDFAIL signal is deactivated as soon as the watchdog connects correctly. If one of the frustration modes described in zone III occurs, the performance of WDFAIL is checked again while the watchdog is fully operational [11]. The edition register is updated with the bombed situation and therefore the idea of disappointment. Watchdog Failure Validation also activates a reset counter for a reinvented time measurement. The length of the counter is generally determined by measuring the troubleshooting data to be cleared. When the counter expires, WDT describes the high performance of RSTOUT. The reset counter will not be practical at power up and therefore the

RSTOUT efficiency will now be set at a low level. When presented to the observer simply because the gauge is finally getting stronger.

Fig 3: A Novel Watchdog Timer Functional Block

# **IV. Simulation Results And Discussion**

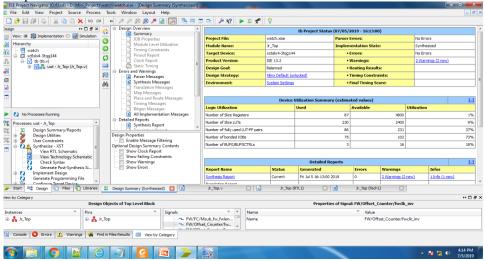

#### **Project Navigator**

Project Navigator is a maximum-level manager of the CPLD design and also Xilinx FPGA, you can do the following. [Sources] to add and create a design source file to be displayed in the window. Edit the source file in the workspace. Run the process of source file in the process window.

Fig 4: Project Navigator

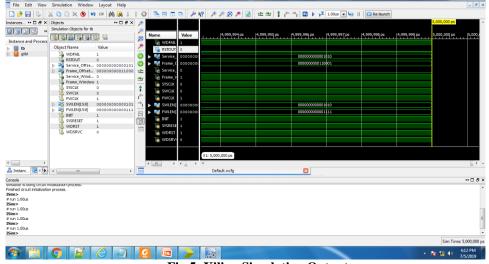

#### **Simulation Output**

**Fig 5: Xilinx Simulation Output**

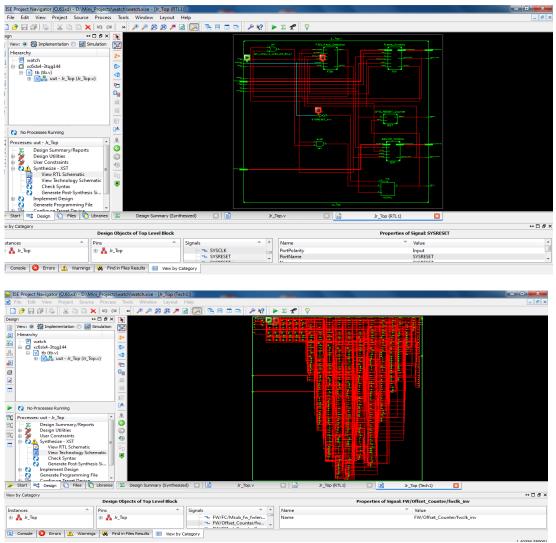

## **Design Objects of Top Level Block Output**

In a run of the mill configuration stream, a FPGA application engineer will reenact the plan at various stages all through the structure procedure. At first the RTL portrayal in VHDL or Verilog is mimicked by making test seats to reenact the framework and watch results. At that point, after the combination motor has mapped the structure to a netlist, the netlist is meant an entryway level portrayal where reenactment is rehashed to affirm the blend continued without blunders. At last the structure is spread out in the FPGA so, all things considered proliferation postponements can be included and the reproduction run again with these qualities back-commented on onto the netlist.

Fig 6: Top Level Block Output using RTL Schematic

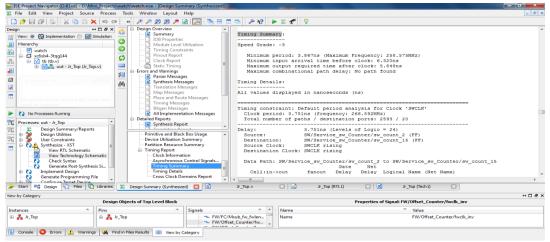

## **Timing Summary**

The Timing Summary segment is a diagram of the plan that incorporates: Timing blunders, which is the combined number of mistakes for the whole structure. Requirements inclusion, which shows the quantity of ways, net and associations secured by limitations.

Fig 7: Timing Design Summary

# V. Conclusion

This paper introduced intimately the engineering and plan of an improved windowed watchdog timer and effecting in FPGA. A watchdog timer runs completely freed from computer and grants altering timer parameters as signify the appliance. A couple of flaw identification measures are included with watchdog first location of inconsistent encoding form. The ability to differentiate frustration style and record it and may get significant as examine. Once recognizing a regret the watchdog timer additionally allow merchandise enough instance for scant troubleshoot information by opening a retune.

## References

- S. N. Chau, L. Alkalai, A. T. Tai, and J. B. Burt, "Design of a fault-tolerant COTS-based bus architecture,"IEEE Transactions on Reliability, vol. 48, no. 4, pp. 351–359, Dec. 1999.

- [2] A. M. El-Attar and G. Fahmy, "An improved watchdog timer to enhance imaging system reliability in the presence of soft errors," in Signal Processing and Information Technology, 2007 IEEE International Symposium on. IEEE, Dec. 2007, pp. 1100–1104.

- [3] M. Pohronsk a and T. Kraj covi c, "FPGA implementation of multiple hardware watchdog timers for enhancing real-time systems security," in EUROCON-International Conference on Computer as a Tool (EURO-CON), 2011 IEEE. IEEE, Apr. 2011, pp. 1–4.

- [4] H. Guzman-Miranda, L. Sterpone, M. Violante, M. A. Aguirre, and M. Gutierrez-Rizo, "Coping with the obsolescence of safety- or mission-critical embedded systems using fpgas,"IEEE Transactions on Industrial Electronics, vol. 58, no. 3, pp. 814–821, 2011.

- [5] H. Amer and A. Sobeih, "Increasing the reliability of the Motorola MC68HC11 in the presence of temporary failures," in Electro technical Conference, 2002. MELECON 2002. 11th Mediterranean. IEEE, May2002, pp. 231–234.

- [6] Karthick, R and Sundararajan, M. (2017), "A Reconfigurable Method for Time Correlated MIMO Channels with a Decision Feedback Receiver," International Journal of Applied Engineering Research, 12.

- [7] Karthick, R and Sundararajan, M.(2017), "PSO based out-of-order (000) execution scheme for HT-MPSOC" Journal of Advanced Research in Dynamical and Control Systems, 9.

- [8] Karthick, R and Sundararajan, M. (2017), "Design and Implementation of Low Power Testing Using Advanced Razor Based Processor," International Journal of Applied Engineering Research,12.

- [9] Karthick, R and Sundararajan, M. (2018), "A novel 3-D-IC test architecture-a review," International Journal of Engineering and Technology (UAE), 7.