# Data storage system of personalized multimedia network teaching resources based on Hypertext

WANG Fei-fei<sup>1</sup>, LIANG Yan<sup>2</sup>

{WANGfeiF06@163.com<sup>1</sup>, LiangYan3263@163.com<sup>2</sup>} <sup>1,2</sup>Jilin International Studies University, Changchun 130000, China;

**Abstract :** The feedback effect of traditional multimedia network teaching resource data storage system is not good, which leads to the incomplete data when students query or download teaching resources. Therefore, a personalized multimedia network teaching resource data storage system based on hypertext is designed. On the basis of the original system hardware, the memory with larger capacity is selected, and the interface of the memory with larger capacity is redesigned; at the same time, the drive circuit of the memory is designed to ensure the smooth operation of the data. In the aspect of software design, by establishing the queuing model of teaching resource storage process, redefining the data storage system design is realized. The experimental results show that the feedback effect of the system is better than that of the traditional data storage system. Therefore, the system can be applied to the current personalized multimedia network teaching.

Keywords: Hypertext; Personalized Multimedia Network Teaching; Resource Data Storage System

# **1** Introduction

The feedback ability of traditional teaching resource data storage system is weak, so in order to ensure teaching resources and teaching level, improve students' learning interest and learning ability, a personalized multimedia network teaching resource data storage system based on hypertext is designed <sup>[1]</sup>. Hypertext is a form of information management technology or electronic document. One of its characteristics is an anti-traditional way of recording information in linear order. It imitates human's associative memory thinking and stores and records the information of teaching resources in a network structure<sup>[2]</sup>.

In the design of multimedia teaching resource storage system, the non-linear technology

of hypertext and hypermedia breaks the linear rule of organizing multimedia information <sup>[3-4]</sup>. According to people's habitual way of thinking, it can build a database feedback mode with strong individualized teaching resource data in the form required by students, and realize data query and download with stronger feedback for students Provide perfect learning tools.

# 2 Hardware Design of Personalized Multimedia Network Teaching Resource Data Storage System

#### 2.1 Selection and Interface Design of Large Capacity Memory

At present, there are two kinds of memory used in embedded storage system: ROM (read-only memory) and RAM (random access memory). Both of them belong to semiconductor memory, ROM can still save data when the system stops power supply, and the data in RAM will be lost after the system is powered off. Considering the importance of personalized multimedia network teaching resources, the most suitable memory for data resource storage system is Flash ROM.

The mainstream flash ROM includes NAND FLASH and NOR FLASH, both of which are fast and safe storage media without data loss due to power failure. NorFlash is characterized by faster reading, smaller capacity and slower writing and erasure, and is suitable for storage of programs and code . Nand Flash's storage unit is serially connected to external pins, and its internally integrated multiplexed ports are used for time-sharing of commands, addresses, and data . It is characterized by fast writing and erasure, large storage capacity, suitable for a system or electronic device that needs a lot of data storage. According to the requirement of rich and diversified teaching resources, the designed data storage system should choose the Nand Flash chip with large data storage capacity, quick response and parallel communication as the large capacity memory of the system. In terms of storage capacity, Nand Flash has 512KB-16GB of different capacity levels to choose from. is divided into MLC (MultiLevel Cell) architecture and SLC (SingleLevel Cell) architecture from the storage cell structure type. The NAND FLASH of the MCL framework can store multi-bit information in each storage unit, and the different data can be accurately stored in the storage unit through the precise control of different potential voltages in the cell. Each unit of the SCL framework, Nand Flash, can store 1-bit information. The advantage of the architecture is that the storage technology is relatively simple and the storage function is relatively fast.

——Based on the specific requirements of the storage system, the storage data capacity needs to reach gb level, but the high temperature Nand Flash that can be purchased on the market at present is only the LHD S 1 GANand Flash chip that qingdao zhiteng company began to

represent at the end of 2017, as shown in figure 1 below:

Figure 1 Physical diagram of large-capacity storage

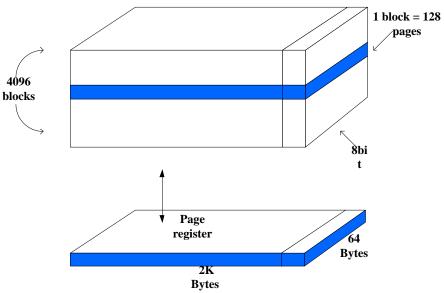

The large-capacity storage in the above picture, its essence is Samsung's K9F8G08UOM type Nand FLASH, but it is encapsulated in the outside and made high temperature gold plating treatment, the maximum working temperature is 175 °C, which meets the temperature requirement of the system hardware under the multimedia long time teaching. K9F8G08UOM is constructed using SCL with a 1 GB of Nand Flash chip with 1 8GB memory chip (8GB for 1G byte) inside, each Chip contains 1 layer (Plane) and each layer contains 4096 storage blocks (Block). The following figure 2 shows the storage array organization diagram of K9F8G08UOM.

#### Fig.2 Structure of memory array

Where Block is the minimum unit for the Nand Flash to perform the erasure operation. each block contains 128 pages (page), each page has (2 k64) bytes storage space, and the page is also the minimum unit for nand flash to program (write in). Therefore, the overall storage capacity of K9F8G08UOM is 8448 Mb, and the conventional storage capacity is 8GB, that is 1 GB.

#### 2.2 Design of memory drive circuits

K9F8G08UOM type Nand Flash has eight command, address, data reuse of the I/O parallel bus interface, can transfer both the instruction of the teaching resources read and write, can also execute the erasure instruction, and can transmit the address of each storage unit, and the read and write data is also transmitted through these eight pins. The unique communication connection of Nand FLASH makes it different from that of Nor FLASH, which requires too many address pins, greatly improves the storage capacity of the memory, simplifies the hardware connection, and liberates the application resources of the main control chip. Its pin function is shown in Table 1 below.:

| Table 1         Nand Flash Pin function parameters |       |                           |  |  |  |

|----------------------------------------------------|-------|---------------------------|--|--|--|

| Serial                                             | Pin   | Pin Function              |  |  |  |

| number                                             | Name  |                           |  |  |  |

| 1                                                  | I/O0- | I/O for command, address, |  |  |  |

|                                                    | I/O7  | data                      |  |  |  |

| 2                                                  | CLE   | Command latch enable      |  |  |  |

| 3                                                  | ALE   | Address latch enable      |  |  |  |

| 4                                                  | CE    | Chip Select Enable        |  |  |  |

| 5                                                  | RE    | Read enable               |  |  |  |

| 6                                                  | WE    | Write enable              |  |  |  |

| 7                                                  | WP    | Write protected           |  |  |  |

| 8                                                  | R/B   | Ready / busy output       |  |  |  |

Table 1

Nand Flash Pin function parameters

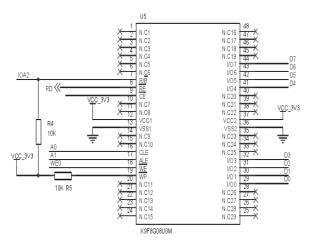

K9F8G08UOM type Nand Flash is powered by 2.7V-3.6V DC voltage. Except for the power supply and the ground, the other angle P is connected to TMS320F28335, of which ALE, CLE are connected to the AO and A1 address lines of TMS320F28335; Read enable end RE, write enable end WE and F28335 DSP external read enable and external write enable respectively. The off-chip storage expansion Zone Zone Zone 7 of the chip selector connection DSP, the R/B pin selects pull up and connects a GPIO port of the DSP, and the write protection side also selects pull up , 8 data lines connected to main control chip data bus. A schematic diagram of the connection is shown in Figure 3 below :

Figure 3 Schematic diagram of the connection

It can be seen from Figure 3 that the design of memory driving circuit ensures the continuous driving ability of the storage system and the smooth operation of data storage, thus realizing the hardware design of personalized multimedia network teaching resources and data storage system.

# **3** Software Design of Teaching Resource Data Storage System Based on Hypertext

Based on the features of hypertext, the software of data storage system is designed to ensure the compatibility between storage system software and hardware.

## 3.1 Establishing the Queuing Model of Teaching Resource Store Process

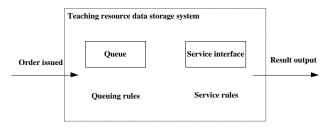

The instructional resource storage queuing model, also called the service model, is used to sort the data of the supertext resource storage order. As we all know, service organization and service object constitute service model together. Service object is operator's command time, and storage system's service time to operator is random. Figure 4 is a schematic diagram of a simple queuing model :

Figure 4 Queuing Model

According to the above figure, the interface between the user and the database is stored

procedure, the user can access the database by calling the stored procedure of different functions, and by establishing the queuing model, the configuration of the stored procedure of the database as the service window is analyzed, so as to arrange the calling program more reasonably to realize the purpose of personalized multimedia network teaching <sup>[5]</sup>

This paper analyzes the user request, storage process and response process, and summarizes the scheduling characteristics of the model according to the characteristics of the queuing model. Take three indicators as an example to describe the input process of the storage system. Suppose for a certain period of time T, As n student users continue to use the teaching resource storage system to query teaching materials, the total number of proposed user sources is infinite, so exist  $n \rightarrow \infty$ ; When the users of the teaching resource data storage system are the f(x) service objects of the queuing model, by default, they come in random order, appear individually and independently of each other; because the users come randomly, appear individually and independently of each other arrival of users can be compared to the input stream  $x_n$ , It is assumed that the service window serving time for each customer and the interval between users' arrival are all negative exponential distribution. In (0,T) time, the number of users arriving is a Poisson process.

Then set the sorting rules of the queuing model. When the user makes an operation request, the storage system first responds to the earliest request. If the stored procedure has been occupied, the user will enter the waiting stage. Therefore, the queuing rule of the system is first come first serve waiting. Suppose that in the storage system, a task is completed by a stored procedure, which completes the request according to the passing of a parameter. According to the above analysis and feature collection, the storage system queuing model can be described as follows:

$$f(x_n) = \sum_{i=1}^m k_i x_n - \sigma_a / q(T) \quad (1)$$

In the formula :  $k_i$  represents the search feature of the *i* th user ;  $\sigma_a$  Y represents the constraints of the *a* user ; *m* is the number of services . After the user puts forward the query operation request, some relevant parameters can be obtained by adding code to the stored procedure to report the execution progress, as shown in Table 2 below:

#### **Table 2 Relevant parameters**

| Average | Average | Average   | Average |

|---------|---------|-----------|---------|

| column  | waiting | length of | waiting |

| length  | column  | stay      | time    |

|         | length  |           |         |

| 27      | 26      | 0.964     | 0.965   |

| 298     | 297     | 0.997     | 0.996   |

| 568     | 567     | 0.998     | 0.998   |

It is assumed that customers arrive according to the Poisson distribution with parameter g, Service time is T, The average service rate is  $\tau$ , make n(T) = L the queue length at L time  $T_1$ , the probability that  $q_n(T) = q\{n(T) = L\}$  represents the queue length of n(T) = L is  $q_n$ . According to the probability theory, we can get the balance equations of the storage system :

$$\begin{cases} q'(T) = -(g + \tau)q_n(T) + gq_{n-b}(T) + \tau q_{n+b}(T) \\ q'_0(T) = -gq_0(T) + gq_b(T) \end{cases}$$

(2)

In the formula: b represents random task requests among n operation requests . when  $T \rightarrow \infty$ , Theoretically, it can be proved that when the storage system is stably distributed. By substituting formula (2) into formula (1), a complete queuing model of teaching resource storage can be obtained.

#### 3.2 Storage function driver technology setting data storage program

According to the NAND flash storage array structure and sorting model, the driver and control program are designed to match the hardware of the storage system to realize the erasure and read-write control of NAND flash. Because there is no NAND flash Hardware Manager in TMS320F28335, it is necessary to develop the corresponding driver of NAND flash to realize the setting of data storage program.

It is known that NAND flash has a variety of data storage methods, including full page writing, single byte writing and other storage methods. At the same time, NAND flash has 8 I / O parallel bus interfaces for command, address and data multiplexing. When using single byte write storage mode, each time data storage is carried out, 8 data lines need to carry out write command transmission and addressing operation. The memory system designed in this paper has a memory space of 1024 bytes per page. If a single byte is used to write the memory, the operation cycle required to write a full page of data is relatively long, and the overall working

efficiency of the system is low. Therefore, the system uses the storage mode of whole page writing to store data, so as to achieve the purpose of relatively fast data storage <sup>[7-9]</sup>.

When storing, the size of each page of the memory is 1024 bytes, and the data structure of each page is designed as follows: the first to the fourth words contain knowledge points and time information, and the later storage space is used to store the notes information of the multi-channel A / D sampling channel of the system to the sensor output. At the same time, in consideration of high-temperature chip cost, the data stored in NAND flash is read out to the on-chip RAM of DSP in turn by using queuing model, and the data in the middle buffer RAM is packaged and read out in turn by using the system development environment CCS. Before the operation of NAND flash, the corresponding operation instructions should be transmitted first, and the corresponding block or page should be addressed. Known operation instructions of LHDs 1 GA NAND flash are shown in Table 3.

| Table 3 Operation instructions |             |              |  |  |

|--------------------------------|-------------|--------------|--|--|

| Features                       | First cycle | Second cycle |  |  |

| Read                           | 00h         | 30h          |  |  |

| Page                           | 80h         | 10h          |  |  |

| programming                    |             |              |  |  |

| Block erase                    | 60h         | D0h          |  |  |

| Reset                          | FFh         | -            |  |  |

NAND flash has a special addressing cycle. It usually takes five cycles to locate a byte in the storage space. Taking LHDs 1 GA NAND flash as an example, the address of the first two cycles is called column address, in which the significant bit is ao-a12, which meets the intra page addressing of lhds1ganand flash (211 = 2048, in which A12 is not used)<sup>[10-12]</sup>. The last three address cycles are called row addresses, which are used for inter page addressing and inter block addressing within blocks. The effective bits are a13-a30. The invalid bits of NAND flash address cycle should be set low, and its addressing cycle is shown in Table 4 below.

| Table 4 Addressing cycle table |     |     |     |     |     |

|--------------------------------|-----|-----|-----|-----|-----|

| Add.                           | 1th | 2th | 3th | 4th | 5th |

| IO0                            | A0  | A8  | A12 | A20 | A28 |

| IO1                            | A1  | A9  | A13 | A21 | A29 |

| IO2                            | A2  | A10 | A14 | A22 | A30 |

| IO3                            | A3  | A11 | A15 | A23 | 0   |

| IO4                            | A4  | 0   | A16 | A24 | 0   |

| IO5                            | A5  | 0   | A17 | A25 | 0   |

| IO6                            | A6  | 0   | A18 | A26 | 0   |

| IO7 A7 0 A19 A27 0 |

|--------------------|

|--------------------|

For the specific operation of NAND flash, first compare the operation instructions in the table, and send the first cycle operation instructions through the command latch enable end cle of NAND flash, and then transmit the address of the storage block or page required for the operation through the address latch enable end of NAND flash. After the operation is completed or the data transmission is completed, the second cycle operation instruction is sent through the command latch enable end cle. At the same time, through the ready / busy status bit R / B to determine whether the operation is completed or not, to achieve the storage system storage program settings

#### 3.3 Hypertext Management Storage System Database

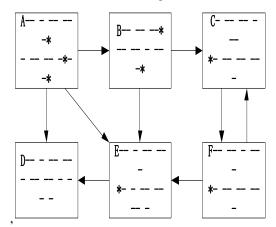

Hypertext Technology is a kind of information management technology. It uses nodes (also known as knowledge points or information blocks) as the basic unit, and organizes nodes into a mesh structure with chains. If the teaching resource data node includes not only text, but also multimedia information such as sound, animation, graphics, image, it is called hypermedia. The hypertext structure is shown in Figure 5 :

Figure 5 Schematic diagram of the hypertext structure

As can be seen from the figure, hypertext structure is composed of several internally interconnected text blocks (or other types of information, so it is generally called information blocks)<sup>[13-15]</sup>. Each node has several pointers to or from other nodes, which are called links. If each text block in Figure 5 is regarded as a node, and each chain (regardless of its specific starting position in the text block) is regarded as a directed edge, then the directed graph as shown in Figure 6 is obtained, which is the topological structure of hypertext.

Figure 6 Topological Structure of Hypertext

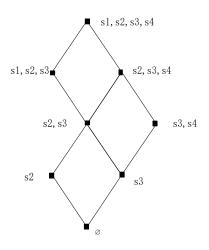

Manage storage system database according to hypertext topology. Suppose  $\{s_1, s_2, s_3, s_4\}$  is an independent knowledge state, and all the knowledge states are known, that is, the set that does not conflict with the premise relationship. The knowledge space of the knowledge domain w is composed of empty set  $\emptyset$  and full set w, The Hasse diagram of the space is shown in Figure 7 below.

Figure 7 Hasse Chart of Knowledge Space for Educational Resources

According to the above analysis, the database planning algorithm is set to control the feedback mode of the storage system database. The calculation equation of the algorithm is:

$$h(\mathcal{G}) = \frac{k + \sqrt{1 - k^2}}{1 + \lambda^{-\mu(\mathcal{G} - k)}} \quad (3)$$

Where:  $\mathcal{G}$  represents the standard value of system feedback capability;; k represents the logical relationship of teaching materials :  $\lambda$  is the general value of database feedback :  $\mu$  is the feedback coefficient. At this point, the management of the storage system database is completed, and the design of personalized multimedia network teaching resource data storage system based on hypertext is realized.

# **4** Testing experiment

The data storage system based on hypertext is verified and tested by Windows operating system, and the system is compared with the data storage system designed by traditional methods to analyze the functional characteristics of the hypertext storage system. Open the multimedia network teaching system, as shown in figure 8 below, upload a large number of teaching resource data to the system, and use it as the basic data source center to design the data storage system.

#### Figure 8 System login interface

Login the system to obtain experimental basic data, using two methods, design personalized multimedia network teaching resources data storage system. 100 students were randomly selected and divided into two experimental groups, group A and group B, of which group A was the test participants of the designed system and group B was the test participants of the traditional system. The results of the experiment are shown in Table 5 and Table 6 below .:

| Table 5 Group A Test Results |                 |               |                 |  |

|------------------------------|-----------------|---------------|-----------------|--|

| Serial number                | Feedback result | Serial number | Feedback result |  |

| M1                           |                 | M11           |                 |  |

| M2                           | $\checkmark$    | M12           | $\checkmark$    |  |

| M3                           | $\checkmark$    | M13           | ×               |  |

| M4                           | $\checkmark$    | M14           | $\checkmark$    |  |

| M5                           | $\checkmark$    | M15           | $\checkmark$    |  |

| M6                           | $\checkmark$    | M16           | $\checkmark$    |  |

| M7                           | $\checkmark$    | M17           | $\checkmark$    |  |

| M8                           | $\checkmark$    | M18           | $\checkmark$    |  |

| M9                           | $\checkmark$    | M19           | $\checkmark$    |  |

| M10           | $\checkmark$    | M20                   |                 |

|---------------|-----------------|-----------------------|-----------------|

|               | Table 6 tes     | st results of group B |                 |

| Serial number | Feedback result | Serial number         | Feedback result |

| N1            |                 | N11                   |                 |

| N2            | ×               | N12                   |                 |

| N3            | $\checkmark$    | N13                   | ×               |

| N4            | $\checkmark$    | N14                   | ×               |

| N5            | ×               | N15                   | $\checkmark$    |

| N6            | ×               | N16                   | $\checkmark$    |

| N7            | ×               | N17                   | ×               |

| N8            | $\checkmark$    | N18                   | $\checkmark$    |

| N9            | $\checkmark$    | N19                   | ×               |

| N10           | $\checkmark$    | N20                   | ×               |

According to the data in the above table, under the same experimental test conditions, the hypertext based data storage system has only one prompt error in its feedback, while the traditional method design data storage system has nine prompt errors in its feedback results. It can be seen that hypertext-based storage systems have better feedback.

## **5** Concluding remarks

The method of designing the data storage system of teaching resources, according to the functional characteristics of hypertext technology, a storage system with better compatibility of software and hardware and stronger feedback ability is designed to ensure that the data can be accurately feedback the data search results through hypertext topology results. However, the design of the storage system is only for the current stage of hardware design, if there is a better performance of hardware, teaching resources data storage system can be re-designed.

## **6** Fund projects

The article is a phased research achievement of the National Computer Basic Education Research Project "Research on the Reform of Computer Practice Teaching System for Liberal Arts Majors in the Perspective of Innovation and Entrepreneurship" (No: 2019-AFCEC-042)

## References

[1] ZHANG Zhedong, TIAN Xia, XIA Xiaoyun, et al. Data Storage System of Ground and Sea Clutter Based on Cluster Architecture, Modern Radar, 41(5):52-57+85 (2019)

[2] LV Wei, WANG Suyao. High-Band width Data Acquisition and Storage System for Three-Dimensional Imaging Lidar . Laser & Optoelectronics Progress, 56(10):259-268 (2019)

[3] HOU Jie. Design of Dynamic Data Storage System for Massive Lidar Data Under Cloud Computing .

Bulletin of Science and Technology ,34(09):201-205 (2018)

[4] LI Haojun, ZHANG Zheng, ZHANG Pengwei. Personalized Learning Resource Recommendation Method Based on Three-dimensional Feature Cooperative Domination . Computer Science, 46(1):461-467 (2019)

[5] SI Yamin, WU Bin. Database Classification Optimization Storage Simulation in Wireless Network.

Computer Simulation, 35(7):355-358+433 (2018)

[6] TIAN Xiping, HUANG Yongjie. Research on Hypertext Query Algorithm for Large Relational Database Based on Association Rules . Bulletin of Science and Technology, 34(10):109-112 (2018)

[7] XU Qiang.The Philosophy of Information and "Digital Wittgenstein Scholarship" . Journal of Guangdong University of Foreign Studies, 30(2):125-131+137 (2019)

[8] WANG Haitao, LI Zhanhuai, ZHANG Xiao, et al. A Performance Optimization Method for Key-Value Store Based on LSM-tree . Journal of Computer Research and Development, ,56(8):1792-1802 (2019)

[9] ZHANG Junxiang, LIU Xinghong, CHEN Mixue, et al. Study on data compatibility between formal learning and informal learning in intelligent learning management system. Journal of Hubei Normal University(Natural Science), 39(2):7-11 (2019)

[10] ZHU Jie, LU Xinghua. Multimedia integrated learning resources information integration system in cloud storage environment . Information Technology,43(6):125-129 (2019)

[11] ZHANG Zhedong, TIAN Xia, XIA Xiaoyun, et al. Data Storage System of Ground and Sea Clutter Based on Cluster Architecture, Modern Radar, 41(5):52-57, 85 (2019)

[12] DU Wenlue, LI Hongwei, GAO Yue. The Design and Implementation of System about Image Data Acquisition and Storage in Underwater Test, Chinese Journal of Electron Devices, 42(3):733-739 (2019).

[12] GUO Hui-yun , FANG Jun , LI Dong . A multi-source streaming data real-time storage system based on load balance , Computer Engineering and Science , 39(4):641-647 (2017)

[13] CHEN Jian-wei, CHEN Hong, WANG Jin-qi, et al. High Reliable Multi-channel Analog Signal Acquisition and Storage System, Instrument Technique and Sensor, 15(3):114-118 (2019).

[14] ZHANG Li-xin, ZHENG Liao-mo, LI Suo. Design and Implementation of Remote Transmission Scheme for Reliability Data of Multi Area Numerical Control System, Modular Machine Tool & Automatic Manufacturing Technique, 32(9):80-83 (2017)

[15] JASON Rhode, STEPHANIE Richter, TRACY Miller. Designing Personalized Online Teaching Professional Development through Self-Assessment. Techtrends, 61(5):1-8 (2017)