# **Review of Network on Chip Routing Algorithms**

Khurshid Ahmad\*, Muhammad Athar Javed Sethi

Department of Computer Systems Engineering, University of Engineering and Technology, Peshawar, Pakistan khurshidkk1989@gmail.com, atharsethi@uetpeshawar.edu.pk

#### Abstract

System on chip (SoC) is an integrated circuit in which components are communicating through the bus interconnection system. Network on chip (NoC) is a communication network for a multiprocessor system on chip (MPSoC). In NoC architecture node/ component of MPSOC are communicating through a network. The performance of NoC architecture depends on topology, routing algorithm and switching technique. In this paper, different NoC routing algorithms are review using basic parameters of NoC architecture and also provide some information about these parameters. It is concluded that most of the researchers are interested in design of the NoC routing algorithm, which efficiently transmits data from source to destination. When the routing algorithm is congestion aware, fault-tolerant, deadlock-free and live-lock free, then the latency of algorithm decreases and throughput increases.

Keywords: System on Chip, Network on Chip, Routing Algorithm.

Received on 07 November 2020, accepted on 11 December 2020, published on 23 December 2020

Copyright © 2020 Khurshid Ahmad *et al.*, licensed to EAI. This is an open access article distributed under the terms of the <u>Creative Commons Attribution license</u>, which permits unlimited use, distribution and reproduction in any medium so long as the original work is properly cited.

doi: 10.4108/eai.23-12-2020.167793

#### **1. Introduction**

The System on Chip (SoC) has a prominent role in the computing world. It is used in mobile computing, embedded system and now also implied to a personal computer such as laptop and tablet PC etc. SoC is a design methodology used by very-large-scale integration (VLSI) designers. The interconnection system of SoC based on share bus or dedicated bus. The basic problem in the bus system as that it allows one communication at the time [1]. Advancement in technology, SoC in an embedded system is increasingly large and complex [2]. Fig (1) shows the interconnection system of SoC in which different devices are connected through a shared bus system. The problem of communication arises because bus architecture cannot meet the requirement like area utilisation, single clock synchronisation, propagation delay, latency, throughput and power consumption [3]. Network on chip (NoC) appear as a better solution for the implementation of SoC [1]. NoC can be defined as "A communication network targeted for onchip communication". NoC is efficient for on-chip communication for SoC [4-6].

Fig (1). Interconnection System of SoC

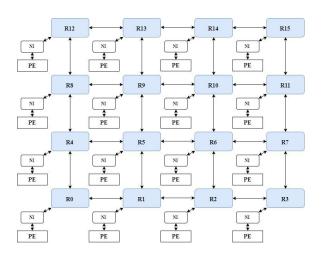

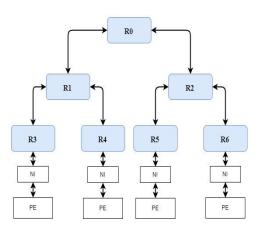

NoC is a communication network between multiple devices. Devices are connected in regular or irregular topology [7-9]. The devices are processor, memory, DSP core etc are called processing element (PE). The PE has two types, homogeneous and heterogeneous. Fig (2) shows 4\*4 mesh topology of NoC. In which PEs are connected to local routers through a network interface (NI) and routers are connected to each other with a point to point connection. The NI transforms the message to packet and packet received by router send it to neighbour router. The packet move to the destination is travelling through routers [10, 11].

#### Fig (2). 4\*4 NoC

The overall performance of NoC depends on topology, routing algorithm, flow control and switching technique [4]. Topology means how nodes are connected in a network. There are different types of topology such as mesh, torus, tree, ring, star, spidergon and also some irregular topology [10]. Routing algorithm defines the path taken by a packet from source to destination. XY, IX/Y, XYX etc. are some example of routing algorithm [4]. There are two major types of switching, circuit switching and packet switching. In circuit switching a physical or virtual link are establishing between source and destination. In packet switching message is divide into packets at source and routed to the destination. The routing algorithm determines a route for packet [3]. The understanding of routing algorithm is very critical in designing of NoC architecture.

Routing algorithms is a key factor affecting NoC network communication. In this review, we compare different routing algorithm on the bases of a basic parameter of NoC architecture. The parameter for the comparison of routing algorithm are topology, routing type, switching technique, packet and flit size, power dissipation, latency, throughput and simulator on which routing algorithm are implemented. The comparison of routing algorithms is shown in Table 1. We believe that this review paper is helpful for the researcher community to resolve routing issue of NoC architecture in future.

The remainder of the paper is organised in such a way that in section 2, we define deadlock, live-lock and starvation situation of routing algorithms. In section 3, different types of routing algorithm are discus. In section 4, we discussed topology and its type. In section 5, we discussed switching technique and also which switching technique is used in the implementation of which routing algorithm. In section 6 and 7, we discussed which one algorithm is congestion aware and which one is faulttolerant. In section 8, the power dissipation of review routing algorithms is the discus. In section 9, latency and through are discus. In section 10, we discussed different simulator on which the review routing algorithms are implemented.

#### 2. Contemplation on the routing algorithm

Every routing algorithm has a different impact on different NoC architecture. It affects different properties of NoC architecture such as latency, throughput and power consumption.

The routing algorithm is similar to routing in any network. Routing algorithm decides path followed by a packet in communication from source to destination [1, 12, 13]. They prevent deadlock, live-lock and starvation situation. Deadlock is cyclic dependency among node making access to resources where no progress can be made. Live-lock as refers to a situation where packet circulates in the network but not reaching to the destination. In starvation packet in buffer request for output channel but output channel also allocated to another packet [1].

#### 3. Routing type

Different types of routing algorithms are developed for the designing of NOC. Routing algorithms are classified on three key characteristics. Which are routing decision, defining path and path length [1, 12]. On the base of the routing decision, there are two types of source and distributed routing. In source, routing path defines by source router and in distributed routing, each router decides the next direction for packet [1]. According to path defining or adaptively, the routing algorithm has two type deterministic and adaptive algorithms. The path is completely determined from source to destination in advance in the deterministic algorithm. There also as another type partially adaptive which restrict some direction [13]. On the base of path length, there are two types minimal and non-minimal. Shortest path selection algorithm is minimal and the longest path selection algorithm is non-minimal [1, 13].

The routing algorithms GOAL, GAL, DyXY, BARP, ADBR, MaS, Fault-tolerant, FAFT, FT-DyXY, Free-rider, Novel Adaptive, Traffic allocator, MCAR, Efficient deadlock-free, ESPDA and Adaptive multipath are adaptive routing algorithm [9, 14-28]. OE and 3DEP are partial adaptive routing algorithm [29, 30]. DyAD and FA-DyAD are adaptive and deterministic [31, 32]. The deterministic routing algorithms are FTXY and ZigZig [33, 34]. Some more classification is possible like congestion aware algorithm, and Fault-Tolerance-routing algorithm will discuss in section 6 and 7.

#### 4. Topology

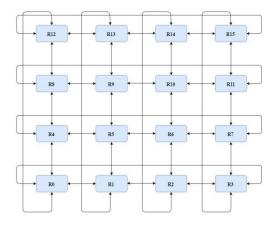

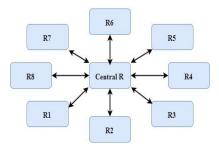

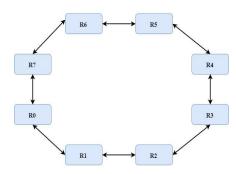

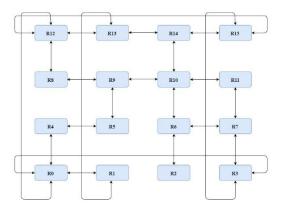

Topology in NoC is an organisation of router and channel. Topology is the roadmap for communication of PE in NoC [35]. It's divide into two types [10]. In regular topology, nodes are connected in a specific pattern. Mesh, torus, star,

ring and tree are popular regular topology [10, 35-38]. The mash topology has M rows and N columns. The intersection of row and column consists of routers and the router are connected to its neighbours. Tours topology are similar to mesh but end routers are connected together with the same row and column routers. In star topology, all routers are connected to a central router. The router is connected to its two neighbours circle shape are ring topology. In tree topology, a child router is connected to its parent router. Fig (3-6) shows the structure of torus, star, ring and tree topology. In irregular, topology nodes are not connected in fix pattern. Fig (7) shows irregular topology.

Fig (3). Torus topology

Fig (4). Star topology

Fig (5). Ring topology

Fig (6). Tree topology

#### Fig (7). irregular topology

To design the routing algorithm for the network, the choosing of topology is the principle step. The performance of the routing algorithm depends on the topology on which it's implemented and also on the number of routers in the topology. When the same algorithm is implemented on mesh  $4\times4$ , and mesh  $8\times8$  have different performance [28]. O1TURN [39], DyXY [16], BARP [18] and FT-XY [33] are implemented on mesh topology having a different number of the router. In this review, Table 1 shows that most of the routing algorithm is implemented on a mesh topology.

## Table 1. NoC Routing algorithm

|      |                                                  | Compression Parameters |                              |                                   |                                                                  |                        |                            |                      |                                                                                     |                                                                        |                                                                    |  |

|------|--------------------------------------------------|------------------------|------------------------------|-----------------------------------|------------------------------------------------------------------|------------------------|----------------------------|----------------------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------|--------------------------------------------------------------------|--|

| S.NO | Algorithm                                        | Year                   | Topology                     | Routing<br>Type                   | Routing<br>characteristic                                        | Switching<br>technique | Packet<br>and flit<br>Size | Power<br>dissipation | Latency                                                                             | Throug<br>hput                                                         | Simulato<br>r                                                      |  |

| 1    | OE<br>[29]                                       | 2000                   | 15×1<br>5 2D<br>mesh         | Partial<br>adaptive               | Deadlock<br>free                                                 | -                      | -                          | -                    | -                                                                                   | -                                                                      | Event-<br>driven<br>simulator                                      |  |

| 2    | GOAL<br>[14]                                     | 2003                   | Torus                        | Adaptive                          | -                                                                | -                      | -                          | -                    | -                                                                                   | -                                                                      | Cycle<br>accurate<br>network<br>simulator                          |  |

| 3    | GAL<br>[15]                                      | 2004                   | 8×8<br>Torus                 | Adaptive                          | Congestion<br>aware                                              | Wormhole               | -                          | -                    | -                                                                                   | -                                                                      | Cycle<br>accurate<br>network<br>simulator                          |  |

| 4    | DyAD<br>[31]                                     | 2004                   | 6×6<br>2D<br>mesh            | Deterministi<br>c and<br>Adaptive | Congestion<br>aware and<br>Deadlock<br>free                      | Wormhole               | -                          | -                    | -                                                                                   | At<br>injecti<br>on rate<br>0.0167<br>are<br>0.027<br>packet/<br>cycle | Worm_si<br>m<br>simulator                                          |  |

| 5    | O1TU<br>RN<br>[39]                               | 2005                   | 4×4,<br>8×8<br>2D<br>mesh    | -                                 | Deadlock<br>free                                                 | -                      | 5 Flit                     | -                    | -                                                                                   | -                                                                      | PoPnet<br>simulator                                                |  |

| 6    | DyXY<br>[16]                                     | 2006                   | 3×3,<br>9×9<br>2D<br>mesh    | Adaptive                          | Congestion<br>aware,<br>deadlock-<br>free and live-<br>lock free | -                      | -                          | -                    | At<br>Average<br>injection<br>rate of<br>0.3 are<br>14<br>Approx.                   | -                                                                      | Event-<br>driven<br>simulator<br>using<br>C++                      |  |

| 7    | Fault<br>aware<br>dynam<br>ic<br>routing<br>[40] | 2008                   | 4×4<br>2D<br>mesh            | -                                 | Fault-tolerant                                                   | Cut<br>through         | 4 flit                     | -                    | When 2<br>fault,<br>injection<br>rate 20<br>flit/node<br>/cycle<br>then 78<br>cycle | -                                                                      | MATLA<br>B<br>Simulink                                             |  |

| 8    | BARP<br>[18]                                     | 2008                   | 8×8,<br>14×1<br>4 2D<br>mesh | Adaptive                          | Deadlock<br>and live-lock<br>free                                | Wormhole               | Flit is<br>16 bit          | -                    | Injectio<br>n rate<br>.25<br>message<br>/cycle<br>then 400<br>cycle                 | -                                                                      | Develope<br>d on flit<br>level<br>NoC<br>simulator<br>using<br>C++ |  |

| 9    | IX/Y<br>[41]                                     | 2008                   | 2D<br>mesh                   | Adaptive                          | Deadlock<br>free                                                 | -                      | -                          | -                    | At injection                                                                        | -                                                                      | Noxim                                                              |  |

|    |                                                    |      |                                                    |                                   |                                         |          |                           |                                                                                          | rate .05                                                                             |                         |                                                                             |

|----|----------------------------------------------------|------|----------------------------------------------------|-----------------------------------|-----------------------------------------|----------|---------------------------|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-------------------------|-----------------------------------------------------------------------------|

|    |                                                    |      |                                                    |                                   |                                         |          |                           |                                                                                          | then<br>below<br>30cycle                                                             |                         |                                                                             |

| 10 | ADBR<br>[17]                                       | 2008 | 8×8<br>2D<br>mesh                                  | Fully<br>adaptive                 | Deadlock<br>free and flow<br>control    | -        | -                         | 0.00035 J                                                                                | at<br>injection<br>rate 0.03<br>are 250<br>cycle                                     | 0.175<br>flit/cyc<br>le | Noxim                                                                       |

| 11 | XYX<br>[42]                                        | 2009 | 2D                                                 | Deterministi<br>c                 | Fault tolerant                          | -        | 32 flit                   | -                                                                                        | -                                                                                    | -                       | VHDL<br>based<br>NoC<br>simulator                                           |

| 12 | FT-XY<br>[33]                                      | 2009 | 5×5,<br>6×6<br>2D<br>mesh                          | Deterministi<br>c                 | Deadlock<br>free                        | -        | -                         | For 6×6<br>Injection<br>rate 0.005-<br>0.009<br>packet/cycl<br>e/node are<br>0.02-0.09 J | For the $6 \times 6$<br>Injectio n rate, 0.03 are 85 cycle Approx.                   | -                       | Noxim                                                                       |

| 13 | DBFA<br>LCI<br>[43]                                | 2009 | 4×4×<br>4 3D<br>Torus                              | -                                 | Live-lock<br>free,<br>Asynchronou<br>s. | -        | -                         | -                                                                                        | -                                                                                    | -                       | OPNET                                                                       |

| 14 | EDXY<br>[44]                                       | 2010 | 7×7,<br>15×1<br>5 2D<br>mesh                       | -                                 | Congestion<br>aware                     | -        | -                         | For 15×15<br>injection<br>rate 9%<br>then<br>26.1197                                     | For 7×7<br>In<br>uniform<br>traffic<br>injection<br>rate<br>28%<br>then 100<br>cycle | -                       | VHDL                                                                        |

| 15 | FA-<br>DyAD<br>[32]                                | 2010 | 6×6<br>2D<br>mesh                                  | Deterministi<br>c and<br>adaptive | Fault and<br>congestion<br>aware        | -        | -                         | -                                                                                        | Fault<br>10%,<br>injection<br>rate .08<br>packet/c<br>ycle<br>then 630<br>approx.    | -                       | gpNocsi<br>m                                                                |

| 16 | Low<br>latency<br>routing<br>algorit<br>hm<br>[45] | 2011 | 3D<br>consi<br>st of<br>4×4<br>2D<br>mesh<br>layer | -                                 | -                                       | -        | -                         | -                                                                                        | -                                                                                    | -                       | Xilinx<br>10.1<br>version<br>is used<br>for<br>simulatio<br>n of<br>results |

| 17 | MaS<br>routing<br>[19]                             | 2012 | 10×1<br>0<br>mesh                                  | Adaptive,<br>buffer less          | Live-lock<br>free                       | Wormhole | 8 flit<br>and 128<br>bit  | At<br>injection<br>rate of 0.21<br>Flit/cycle/n<br>ode are<br>6.5w                       | Average<br>latency<br>of 53<br>cycle                                                 |                         | On-chip<br>network<br>simulator                                             |

| 18 | Fault-<br>toleran<br>t                             | 2012 | 8×8<br>2D<br>mesh                                  | Adaptive                          | -                                       | -        | 16 flit<br>and 128<br>bit | -                                                                                        | -                                                                                    | -                       | XMulato<br>r                                                                |

|    | routing                                             |      |                                         |                   |                                 |          |                                              |                                      |                                                           |                                          |                                                                   |

|----|-----------------------------------------------------|------|-----------------------------------------|-------------------|---------------------------------|----------|----------------------------------------------|--------------------------------------|-----------------------------------------------------------|------------------------------------------|-------------------------------------------------------------------|

|    | routing [9]                                         |      |                                         |                   |                                 |          |                                              |                                      |                                                           |                                          |                                                                   |

| 19 | CATR<br>A [46]                                      | 2012 | 8×8,<br>14×1<br>4 2D<br>mesh            | -                 | Congestion<br>aware             | -        | 1-5 flit<br>distribut<br>ed<br>uniform<br>ly | 2.51w                                | At<br>injection<br>rate 0.35<br>f/n/c are<br>200<br>cycle | -                                        | Impleme<br>nted<br>through<br>VHDL                                |

| 20 | Precon<br>certed<br>wormh<br>ole<br>routing<br>[47] | 2012 | -                                       | -                 | Based on the<br>virtual circuit | wormhole | -                                            | -                                    | -                                                         | -                                        | NIRGA<br>M                                                        |

| 21 | FAFT<br>routing<br>[20]                             | 2013 | 4×4×<br>3 3D<br>mesh                    | Fully<br>adoptive | Fault-tolerant                  | -        | -                                            | -                                    | -                                                         | -                                        | Noxim                                                             |

| 22 | FT-<br>DyXY<br>Z [21]                               | 2014 | 3D<br>mesh                              | Adaptive          | Fault-tolerant                  | -        | 5 flit                                       | -                                    | -                                                         | -                                        | Booksim                                                           |

| 23 | Free-<br>Rider<br>[22]                              | 2014 | 16×1<br>6 2D<br>mesh                    | Adaptive          | Congestion<br>aware             |          | 5 flit<br>and 128<br>bit                     |                                      |                                                           |                                          | Booksim                                                           |

| 24 | Novel<br>adaptiv<br>e<br>routing<br>[23]            | 2015 | 8×8×<br>4,<br>16×1<br>6×1<br>3D<br>mesh | Adaptive          | Congestion<br>aware             | -        | -                                            | At<br>injection<br>rate 0.5 are<br>1 | At<br>injection<br>rate 0.5<br>are 1                      | At<br>injecti<br>on rate<br>0.5 are<br>1 | Noxim                                                             |

| 25 | Distan<br>ce<br>predict<br>ion<br>XY<br>[48]        | 2015 | 2D<br>mesh                              | -                 | -                               | -        | 2-10 flit                                    | -                                    | -                                                         | -                                        | System C<br>platform                                              |

| 26 | DRTL<br>[49]                                        | 2016 | 4×4×<br>4 3D<br>mesh                    | -                 | Deadlock<br>free                | Wormhole | 5 flit<br>and 64<br>bit                      | -                                    | -                                                         | -                                        | Alpha<br>EV6 core<br>model is<br>used<br>result<br>simulatio<br>n |

| 27 | Traffic<br>allocati<br>on<br>routing<br>[24]        | 2016 | 6×6<br>2D<br>mesh                       | Adaptive          | -                               | -        | A<br>packet<br>is 20<br>bytes                | When load<br>50% then<br>61.973 mw   | When<br>load<br>50%<br>then<br>45.9084<br>cycle/fli<br>t  | -                                        | NIRGA<br>M                                                        |

| 28 | MCAR<br>[27]                                        | 2017 | 8×8,<br>16×1<br>6 2D<br>mesh            | Adaptive          | Congestion<br>aware             | -        | -                                            | 7.85% on<br>average                  | -                                                         | 5.84%<br>on<br>averag<br>e               | Booksim<br>2.0                                                    |

| 29 | Efficie<br>nt<br>deadlo<br>ck-free<br>adaptiv       | 2017 | 4×4×<br>4,<br>8×8×<br>4 3D<br>mesh      | Adaptive          | Dead lock-<br>free              | -        | A<br>packet<br>is 8 bit                      | -                                    | -                                                         | -                                        | Noxim                                                             |

|    | e [26]                                |      |                           |                                                     |                                                   |          |                         |                                      |                                                       |                                                       |                                                                              |

|----|---------------------------------------|------|---------------------------|-----------------------------------------------------|---------------------------------------------------|----------|-------------------------|--------------------------------------|-------------------------------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------|

| 30 | ESPA<br>DA<br>[25]                    | 2017 | 8×8<br>2D<br>mesh         | Fully<br>adaptive<br>based on<br>virtual<br>channel | Dead lock-<br>free                                | -        | 5 flit<br>and 64<br>bit | -                                    | -                                                     | -                                                     | GPU<br>based on<br>cyclic<br>accurate<br>NoC                                 |

| 31 | ZigZig<br>[34]                        | 2017 | 2D<br>mesh                | deterministi<br>c                                   | -                                                 | -        | Packet<br>is<br>20bytes | The load is<br>50% then<br>62.698 mw | Average<br>latency<br>is<br>46.2517<br>cycle/fli<br>t | -                                                     | NIRGA<br>M                                                                   |

| 32 | Adapti<br>ve<br>multip<br>ath<br>[28] | 2018 | 4×4,<br>8×8<br>2D<br>mesh | Adaptive                                            | Congestion<br>aware                               | -        | 8 flit<br>and 32<br>bit | -                                    | For 4×4<br>Load<br>0/9<br>GB/sec<br>330 Ns            | -                                                     | HNOC<br>based on<br>OMNET<br>++                                              |

| 33 | Link-<br>Sharin<br>g [50]             | 2018 | 8×8<br>2D<br>mesh         | -                                                   | Congestion<br>aware                               | Wormhole | Flit is<br>32 bit       | 2.86 mw                              | -                                                     | -                                                     | RTL<br>level by<br>using<br>VHDL                                             |

| 34 | UMF<br>[51]                           | 2019 | Mesh                      | -                                                   | Dead lock<br>free                                 | -        | 5 flit                  | -                                    | -                                                     | -                                                     | PopNet                                                                       |

| 35 | TBTF<br>TA<br>[52]                    | 2019 | 8×8<br>2D<br>mesh         | -                                                   | Congestion<br>aware,<br>thermal-fault<br>tolerant | -        | -                       | -                                    | -                                                     | Offer<br>load<br>increas<br>es high<br>throug<br>hput | OPNET                                                                        |

| 36 | 3DEP<br>[30]                          | 2019 | 3D<br>mesh                | Partially<br>adaptive                               | Dead lock<br>free                                 | -        | -                       | -                                    | -                                                     | -                                                     | Noxim                                                                        |

| 37 | CFPA<br>[53]                          | 2019 | Mesh<br>and<br>torus      | -                                                   | Congestion<br>aware, fault-<br>tolerant           | -        | -                       | -                                    | -                                                     | -                                                     | HNOC<br>for<br>algorithm<br>and MC<br>used for<br>circuit-<br>level<br>delay |

## 5. Switching Technique

Switching technique refers to the flow control mechanism of messages between routers. The basic switching techniques that are used in NoC is circuit switching and packet switching. Packet switching is further divided into three broad categories wormhole, store and forward and virtual cut through [10, 54]. In the wormhole, the packet is divided into flit (head flit, body flit and tail flit). Head flit contains source and destination information, body flit contains data which is transmitted to destination and tail flit contain ending information of flit. Due to the pipelined nature of wormhole, it redacts message latency [31, 54, 55]. In store and forward technique, the whole packet is store in the router then routed to the next router. In virtual cut through,

the packet is forwarded to the next router if it ensures that the whole packet is store in it [10, 54].

Due to pipeline nature and low latency wormhole switching technique are preferring in designing of routing algorithm. The GAL, DyAD, BARP, MaS, Preconcerted wormhole routing, DTRL and Link sharing are implemented using wormhole switching technique [15, 18, 19, 31, 47, 49, 50].

## 6. Congestion Awareness

It's characteristic of routing algorithm which improves the performance of NoC by distributing the load over network

and send the traffic over the less congested area. On congestion awareness basis routing algorithm are divided into two types. Congestion oblivious algorithm and congestion aware algorithm [46, 56]. Congestion oblivious algorithm is unable to balance the load over the network and can't consider the congestion status of the network. Without congestion awareness interconnection system of the network is unbalanced and burst. On the other hand, the congestion aware algorithm routes the traffic through the largest available virtual channel.

Table 1 show that GAL, DyAD, DyXY, BARP, EDXY, FA-DyAD, CATRA, Free-Rider, Novel adaptive routing, DTRL, MCAR, Adaptive multipath, Link sharing and CFPA are congestion aware algorithms [15, 16, 20, 22, 27, 28, 31, 32, 44, 46, 50, 52, 53]. Congestion awareness decrees latency and increases throughput. Congestion aware algorithms are further divided on the base of sharing of congestion information are local and non-local [22].

## 7. Fault tolerance

Fault tolerance is network property to examine the functioning of the network component and remains its functioning when some components are inactive/faulty. Fault can occur as a result of a defect in the system, improper environment and improper design of a system. Fault in NoC is categories in two groups on the base of time and occurrence. Hardware fault occurs due to hardware fault of the system and for its removing extra hardware or resources are required [57-59]. The soft fault is denoted by a bug in the software and it can be addressed by routing algorithm.

Scientists and researchers propose different fault-tolerant routing to overcome fault in NoC [10, 60]. A routing algorithm for fault tolerance is Fault aware dynamic routing, FA-DyAD, FAFT routing, FT-DyXY, TBTFTA and CFPA [20, 21, 32, 40, 52, 53]. The compression of these algorithms is shown in table 1.

## 8. Power Dissipation

In the designing of the routing algorithm, the power dissipation is under consideration of scientists and researchers. Power dissipation is divide into two parts; static and dynamic. Static power relates to manufacturing technology and dynamic power depends on the router activity [61]. In [62-66] are the technique are proposed to reduce power consumption.

The power consumption of FT-XY under uniform traffic of 4×4 NoC is .01 to .09 J and for 6×6 NoC its .02 to .09 J for injection rate of .005 to .019 packet/cycle/node [33]. The power consumption for ADBR is .00035J, for MaS algorithm it's a 6.5w at injection rate of 0.21 packet/cycle/node, for Traffic allocation routing algorithm it's 61.973mw when load is 50%, for ZigZig algorithm it's 62.698mw when load is 50% and for Link sharing algorithm it's 2.86mw [17, 19, 24, 34, 50].

## 9. Latency and Throughput

The performance of the routing algorithm depends on latency and throughput. The performance of routing is batter when its latency is low, and throughput is high. Most of the researchers compare their own proposed routing algorithm latency and throughput with other routing algorithms for performance evaluation. Throughput of CFPA is compared with XY and DyAD and shown that its throughput is better than XY and DyAD [53].

The latency and throughput of routing algorithm depend on the number of tiles in NoC, e.g. for same algorithm latency and throughput for 4×4 and 8×8 are different. When the number of tiles in NoC increases the latency of routing algorithm increase and throughput is decrees [23, 28, 34, 44]. Latency and throughput of routing algorithm also depend on the injection rate [16, 18, 32, 40]. Latency and throughput of the review routing algorithms are shown in Table 1.

## **10. Simulator**

There are three approaches for the to evaluate the performance of the system

- Actual system monitoring

- Mathematical modelling

- Simulation modelling

The simulation environment provides an extensible framework for NoC evaluation and provides more feature, different topology, swathing technique, routing algorithm, flow control polices and high accuracy [67-69].

In this review, Table 1 shows most of the routing algorithm performance is evaluated on Noxim, Booksim and NIGRAM simulator. Noxim simulator is used for the performance evaluation of ADBR, FT-XY, FAFT routing algorithm, Novel adaptive routing, Efficient deadlock-free adaptive routing and 3DEP. Booksim simulator is used for FT-DyXY, free-rider and MCAR. Precocerted wormhole routing, traffic allocation routing and ZigZig routing algorithm performance are evaluated through NIGRAM simulator. Some other simulator Event-driven, XMultar, PopNET, gpNoCsim, OpNET, Matlab simulator and eventdriven are used for performance evaluation of routing algorithms.

## **11. Conclusion**

This paper review different routing algorithm of NoC on the base of different parameter. In our view, it's helpful for the researcher community to find and resolve the unanswered issue of this area. Based on Table 1, it is concluded that most of the researchers are interested in to design the routing algorithm, which has low latency, high throughput, low power consumption, congestion aware and faulttolerant. From this review it is concluded that, in the designing of routing algorithm the designers/researchers should compromise on some parameters. When the

algorithm is congestion aware, fault- tolerant, dead lock free and live-lock free than power consumption, area utilisation

## References

- A. V. de Mello, L. C. Ost, F. G. Moraes, and N. L. V. Calazans, "Evaluation of routing algorithms on mesh based nocs," *PUCRS*, *Av. Ipiranga*, p. 22, 2004.

- [2] A. Mejia, M. Palesi, J. Flich, S. Kumar, P. López, R. Holsmark, et al., "Region-based routing: a mechanism to support efficient algorithms in NoCs." routing IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 17, pp. 356-369, 2009.

- [3] G. Adamu, M. P. Chejara, and A. B. Garko, "Review of Deterministic Routing Algorithm For Network-On-Chip," in 2nd international conference on science, technology and management, 2015, pp. 741-745.

- [4] S. D. Chawade, M. A. Gaikwad, and R. M. Patrikar, "Review of XY routing algorithm for network-on-chip architecture," *International Journal of Computer Applications*, vol. 43, pp. 975-8887, 2012.

- [5] P. Guerrier and A. Greiner, "A generic architecture for on-chip packet-switched interconnections," in *Proceedings of the conference on Design, automation and test in Europe*, 2000, pp. 250-256.

- [6] S. Kumar, A. Jantsch, J.-P. Soininen, M. Forsell, M. Millberg, J. Oberg, et al., "A network on chip architecture and design methodology," in Proceedings IEEE Computer Society Annual Symposium on VLSI. New Paradigms for VLSI Systems Design. ISVLSI 2002, 2002, pp. 117-124.

- [7] D. Atienza, F. Angiolini, S. Murali, A. Pullini,

L. Benini, and G. De Micheli, "Network-onchip design and synthesis outlook," *Integration*, vol. 41, pp. 340-359, 2008.

- [8] P. Liu, B. Xia, C. Xiang, X. Wang, W. Wang, and Q. Yao, "A networks-on-chip architecture design space exploration-the LIB," *Computers & Electrical Engineering*, vol. 35, pp. 817-836, 2009.

- [9] F. Safaei and M. ValadBeigi, "An efficient routing methodology to tolerate static and dynamic faults in 2-D mesh networks-on-

and some other parameter like processing are increase but the latency is decrease and throughput is increase.

- chip," *Microprocessors and Microsystems,* vol. 36, pp. 531-542, 2012.

- [10] M. Athar Javed Sethi, F. Azmadi Hussin, and N. Hisham Hamid, "Review of network on chip architectures," *Recent Advances in Electrical & Electronic Engineering (Formerly Recent Patents on Electrical & Electronic Engineering)*, vol. 10, pp. 4-29, 2017.

- [11] C. Wang, W.-H. Hu, S. E. Lee, and N. Bagherzadeh, "Area and power-efficient innovative congestion-aware Network-on-Chip architecture," *Journal of Systems Architecture*, vol. 57, pp. 24-38, 2011.

- [12] G. Adamu, P. Chejara, and A. B. Garko, "Review of Deterministic Routing Algorithm For Network-On-Chip," in 2nd international conference on science, technology and management, 2015, pp. 741-745.

- P. Parandkar, J. Dalal, and S. Katival, "Performance Comparison of XY, OE and DY Ad Routing Algorithm by Load Variation Analysis of 2-Dimensional Mesh Topology Based Network-on-Chip," *BIJIT Journal*, vol. 4, pp. 391-396, 2012.

- [14] A. Singh, W. J. Dally, A. K. Gupta, and B. Towles, "GOAL: a load-balanced adaptive routing algorithm for torus networks," in 30th Annual International Symposium on Computer Architecture, 2003. Proceedings., 2003, pp. 194-205.

- [15] A. Singh, W. J. Dally, B. Towles, and A. K. Gupta, "Globally adaptive load-balanced routing on tori," *IEEE computer architecture letters*, vol. 3, pp. 2-2, 2004.

- [16] M. Li, Q.-A. Zeng, and W.-B. Jone, "DyXY: a proximity congestion-aware deadlock-free dynamic routing method for network on chip," in *Proceedings of the 43rd annual Design Automation Conference*, 2006, pp. 849-852.

- [17] X. Canwen, Z. Minxuan, D. Yong, and Z. Zhitong, "Dimensional bubble flow control and fully adaptive routing in the 2-d mesh network on chip," in 2008 IEEE/IFIP International Conference on Embedded and Ubiquitous Computing, 2008, pp. 353-358.

- [18] P. Lotfi-Kamran, M. Daneshtalab, C. Lucas, and Z. Navabi, "BARP-a dynamic routing protocol for balanced distribution of traffic

in NoCs," in 2008 Design, Automation and Test in Europe, 2008, pp. 1408-1413.

- [19] J. Lin, X. Lin, and L. Tang, "Making-a-stop: A new bufferless routing algorithm for onchip network," *Journal of Parallel and Distributed Computing*, vol. 72, pp. 515-524, 2012.

- [20] X. Jiang and T. Watanabe, "A novel fully adaptive fault-tolerant routing algorithm for 3d network-on-chip," in 2013 IEEE International Conference of IEEE Region 10 (TENCON 2013), 2013, pp. 1-4.

- [21] H. N. Jouybari and K. Mohammadi, "A low overhead, fault tolerant and congestion aware routing algorithm for 3D mesh-based Network-on-Chips," *Microprocessors and Microsystems*, vol. 38, pp. 991-999, 2014.

- [22] S. Liu, T. Chen, L. Li, X. Li, M. Zhang, C. Wang, et al., "FreeRider: non-local adaptive network-on-chip routing with packetcarried propagation of congestion information," *IEEE Transactions on Parallel* and Distributed Systems, vol. 26, pp. 2272-2285, 2014.

- [23] L. Zeng, T. Pan, X. Jiang, and T. Watanabe, "A performance enhanced adaptive routing algorithm for 3D Network-on-Chips," in *TENCON 2015-2015 IEEE Region 10 Conference*, 2015, pp. 1-4.

- [24] N. Wang and P. Valencia, "Traffic Allocation: An efficient adaptive network-on-chip routing algorithm design," in 2016 2nd IEEE International Conference on Computer and Communications (ICCC), 2016, pp. 2015-2019.

- [25] A. Charif, A. Coelho, N.-E. Zergainoh, and M. Nicolaidis, "Mini-espada: A low-cost fully adaptive routing mechanism for networkson-chips," in 2017 18th IEEE Latin American Test Symposium (LATS), 2017, pp. 1-4.

- [26] J. Dai, X. Jiang, R. Li, and T. Watanabe, "An Efficient Deadlock-Free Adaptive Routing Algorithm for 3D Network-on-Chips," in 2017 IEEE 11th International Symposium on Embedded Multicore/Many-core Systemson-Chip (MCSoC), 2017, pp. 29-36.

- [27] R. Xie, J. Cai, X. Xin, and B. Yang, "MCAR: Non-local adaptive Network-on-Chip routing with message propagation of congestion information," *Microprocessors*

*and Microsystems,* vol. 49, pp. 117-126, 2017.

- [28] F. Shafiei and V. Sattari-Naeini, "Development of an Adaptive Multipath Routing Algorithm by Examining the Congestion and Channel Fault of One-Hop Nodes in Network-on-Chip," in 2018 8th International Conference on Computer and Knowledge Engineering (ICCKE), 2018, pp. 231-236.

- [29] G.-M. Chiu, "The odd-even turn model for adaptive routing," *IEEE Transactions on parallel and distributed systems,* vol. 11, pp. 729-738, 2000.

- [30] F. Vahdatpanah, M. Elahi, S. Kashi, E. Taheri, and A. Patooghy, "3DEP: A Efficient Routing Algorithm to Evenly Distribute Traffic Over 3D Network-on-Chips," in 2019 27th Euromicro International Conference on Parallel, Distributed and Network-Based Processing (PDP), 2019, pp. 237-241.

- [31] J. Hu and R. Marculescu, "DyAD: smart routing for networks-on-chip," in *Proceedings of the 41st annual Design Automation Conference*, 2004, pp. 260-263.

- [32] A. Mehranzadeh, A. Khademzadeh, and A. Mehran, "FADyAD-fault and congestion aware routing algorithm based on DyAD algorithm," in 2010 5th International Symposium on Telecommunications, 2010, pp. 274-279.

- [33] M. Valinataj, S. Mohammadi, S. Safari, and J. Plosila, "A link failure aware routing algorithm for Networks-on-Chip in nano technologies," in 2009 9th IEEE Conference on Nanotechnology (IEEE-NANO), 2009, pp. 687-690.

- [34] P. Valencia, E. Muller, and N. Wang, "ZigZag: An efficient deterministic Network-on-chip routing algorithm design," in 2017 8th IEEE Annual Information Technology, Electronics and Mobile Communication Conference (IEMCON), 2017, pp. 1-5.

- [35] T. N. K. Reddy, A. K. Swain, J. K. Singh, and K. K. Mahapatra, "Performance assessment of different Network-on-Chip topologies," in 2014 2nd International Conference on Devices, Circuits and Systems (ICDCS), 2014, pp. 1-5.

- [36] J. Chen, C. Li, and P. Gillard, "Network-onchip (NoC) topologies and performance: a review," in *Proceedings of the 2011 Newfoundland Electrical and Computer Engineering Conference (NECEC)*, 2011, pp. 1-6.

- [37] A. Kalita, K. Ray, A. Biswas, and M. A. Hussain, "A topology for network-on-chip," in 2016 International Conference on Information Communication and Embedded Systems (ICICES), 2016, pp. 1-7.

- [38] Y. Salah, M. Atri, and R. Tourki, "Design of a 2d mesh-torus router for network on chip," in 2007 IEEE International Symposium on Signal Processing and Information Technology, 2007, pp. 626-631.

- [39] D. Seo, A. Ali, W.-T. Lim, and N. Rafique, "Near-optimal worst-case throughput routing for two-dimensional mesh networks," in 32nd International Symposium on Computer Architecture (ISCA'05), 2005, pp. 432-443.

- [40] A. Hosseini, T. Ragheb, and Y. Massoud, "A fault-aware dynamic routing algorithm for on-chip networks," in 2008 IEEE International Symposium on Circuits and Systems, 2008, pp. 2653-2656.

- [41] A. M. Shafiee, M. Montazeri, and M. Nikdast, "An innovational intermittent algorithm in networks-on-chip (noc)," *ICCSE2008, Paris,* 2008.

- [42] A. Patooghy and S. G. Miremadi, "XYX: A power & performance efficient fault-tolerant routing algorithm for network on chip," in 2009 17th Euromicro International Conference on Parallel, Distributed and Network-based Processing, 2009, pp. 245-251.

- [43] K. Wang, C. Wang, and H. Gu, "Quality of service routing algorithm in the torusbased network on chip," in 2009 IEEE 8th International Conference on ASIC, 2009, pp. 952-954.

- P. Lotfi-Kamran, A.-M. Rahmani, M. Daneshtalab, A. Afzali-Kusha, and Z. Navabi, "EDXY–A low cost congestion-aware routing algorithm for network-on-chips," *Journal of Systems Architecture*, vol. 56, pp. 256-264, 2010.

- [45] A. V. V. Rose, R. Seshasayanan, and G. Oviya, "Fpga implementation of low latency routing algorithm for 3d network on chip," in 2011 International Conference on Recent Trends in Information Technology (ICRTIT), 2011, pp. 385-388.

- [46] M. Ebrahimi, M. Daneshtalab, P. Liljeberg, J. Plosila, and H. Tenhunen, "CATRAcongestion aware trapezoid-based routing algorithm for on-chip networks," in 2012 Design, Automation & Test in Europe Conference & Exhibition (DATE), 2012, pp. 320-325.

- [47] W. Hao and W. Ling, "Preconcerted wormhole routing algorithm for Mesh structure based on the network on chip," in 2012 International Conference on Information Management, Innovation Management and Industrial Engineering, 2012, pp. 154-158.

- [48] W. Ni and Z. Liu, "A routing algorithm for Network-on-Chip with self-similar traffic," in 2015 IEEE 11th International Conference on ASIC (ASICON), 2015, pp. 1-4.

- [49] J. Wang, H. Gu, K. Wang, Y. Yang, and K. Wang, "DRTL: A heat-balanced deadlockfree routing algorithm for 3D topology network-on-chip," *Microprocessors and Microsystems*, vol. 45, pp. 95-104, 2016.

- [50] C. Chen, Q. Li, N. Li, H. Liu, and Y. Dai, "Link-Sharing: Regional Congestion Aware Routing in 2D NoC by Propagating Congestion Information on Idle Links," in 2018 IEEE 3rd International Conference on Integrated Circuits and Microsystems (ICICM), 2018, pp. 291-297.

- [51] Y. Song and B. Lin, "Uniform Minimal First: Latency Reduction in Throughput-Optimal Oblivious Routing for Mesh-Based Networks-on-Chip," *IEEE Embedded Systems Letters*, vol. 11, pp. 81-84, 2019.

- [52] L. Zhu and H. Gu, "A Traffic-Balanced and Thermal-Fault Tolerant Routing Algorithm for Optical Network-on-Chip," in 2019 18th International Conference on Optical Communications and Networks (ICOCN), 2019, pp. 1-3.

- [53] S. T. Muhammad, M. Saad, A. A. El-Moursy, M. A. El-Moursy, and H. F. Hamed, "CFPA: Congestion aware, fault tolerant and

process variation aware adaptive routing algorithm for asynchronous Networks-on-Chip," *Journal of Parallel and Distributed Computing*, vol. 128, pp. 151-166, 2019.

- [54] D. S. D. T. P. S. R. B. Rajesh Singh Thakur, "Network Switching: Traditional Techniques and Evolution," *International Journal of Engineering and Computer Science*, vol. 5, 05/02 2016.

- [55] P. Guerrier and A. Greiner, "A generic architecture for on-chip packet-switched interconnections," in *Design, Automation, and Test in Europe*, 2008, pp. 111-123.

- [56] P. Gratz, B. Grot, and S. W. Keckler, "Regional congestion awareness for load balance in networks-on-chip," in 2008 IEEE 14th International Symposium on High Performance Computer Architecture, 2008, pp. 203-214.

- [57] M. Ali, M. Welzl, and S. Hessler, "A fault tolerant mechanism for handling permanent and transient failures in a network on chip," in *Fourth International Conference on Information Technology* (*ITNG'07*), 2007, pp. 1027-1032.

- [58] T. Lehtonen, D. Wolpert, P. Liljeberg, J. Plosila, and P. Ampadu, "Self-adaptive system for addressing permanent errors in on-chip interconnects," *IEEE Transactions* on Very Large Scale Integration (VLSI) Systems, vol. 18, pp. 527-540, 2009.

- [59] Y.-C. Chang, C.-T. Chiu, S.-Y. Lin, and C.-K. Liu, "On the design and analysis of fault tolerant NoC architecture using spare routers," in 16th Asia and South Pacific Design Automation Conference (ASP-DAC 2011), 2011, pp. 431-436.

- [60] M. A. J. Sethi, F. A. Hussin, and N. H. Hamid, "Implementation of biological sprouting algorithm for NoC fault tolerance," in 2013 IEEE International Conference on Circuits and Systems (ICCAS), 2013, pp. 39-44.

- [61] D. Zhu, Y. Li, and L. Chen, "On Trade-off Between Static and Dynamic Power Consumption in NoC Power Gating," in 2019 IEEE/ACM International Symposium on Low Power Electronics and Design (ISLPED), 2019, pp. 1-6.

- [62] H. Matsutani, M. Koibuchi, D. Ikebuchi, K. Usami, H. Nakamura, and H. Amano, "Ultra

fine-grained run-time power gating of onchip routers for CMPs," in 2010 Fourth ACM/IEEE International Symposium on Networks-on-Chip, 2010, pp. 61-68.

- [63] N. Madan, A. Buyuktosunoglu, P. Bose, and M. Annavaram, "A case for guarded power gating for multi-core processors," in 2011 IEEE 17th International Symposium on High Performance Computer Architecture, 2011, pp. 291-300.

- [64] L. Chen and T. M. Pinkston, "Nord: Noderouter decoupling for effective powergating of on-chip routers," in 2012 45th Annual IEEE/ACM International Symposium on Microarchitecture, 2012, pp. 270-281.

- [65] R. Das, S. Narayanasamy, S. K. Satpathy, and R. G. Dreslinski, "Catnap: Energy proportional multiple network-on-chip," ACM SIGARCH Computer Architecture News, vol. 41, pp. 320-331, 2013.

- [66] S. Yue, L. Chen, D. Zhu, T. M. Pinkston, and M. Pedram, "Smart butterfly: reducing static power dissipation of network-on-chip with core-state-awareness," in *Proceedings* of the 2014 international symposium on Low power electronics and design, 2014, pp. 311-314.

- [67] L. Jain, B. Al-Hashimi, M. Gaur, V. Laxmi, and A. Narayanan, "NIRGAM: a simulator for NoC interconnect routing and application modeling," in *Design, automation and test in Europe conference*, 2007, pp. 16-20.

- [68] A. Nayebi, S. Meraji, A. Shamaei, and H. Sarbazi-Azad, "Xmulator: a listener-based integrated simulation platform for interconnection networks," in *First Asia International Conference on Modelling & Simulation (AMS'07)*, 2007, pp. 128-132.

- [69] Y. Ben-Itzhak, E. Zahavi, I. Cidon, and A. Kolodny, "HNOCS: modular open-source simulator for heterogeneous NoCs," in 2012 international conference on embedded computer systems (SAMOS), 2012, pp. 51-57.