# Low Leakage-Power SRAM Cell Design Using CNTFETs at 32nm Technology

Rajendra Prasad S.<sup>1</sup>, B.K. Madhavi<sup>2</sup>, and K. Lal Kishore<sup>3</sup>

<sup>1</sup> ACE Engineering College, Hyderabad, A.P, India srprasad447@gmail.com <sup>2</sup> AGCET, Keesara, Hyderabad, A.P, India <sup>3</sup> JNT University, Hyderabad, A.P, India

**Abstract.** Leakage power accounts for an increasingly larger portion of total power consumption in nanometer technologies. Battery powered devices remains idle for most of the time except when in use. However, since the phone remains on, it drains power from the battery. This in-turn reduces battery life. In such a situation, battery power can be saved by shutting down the power supply to the circuit when not in operation. This paper proposes ultra-low power Carbon Nanotube Field-Effect Transistor (CNTFET) based SRAM cell to minimize static power dissipation due to leakage. A Sleep Transistor technique is applied to CNTFET based SRAM cell to reduce leakage power. This method reduces leakage power by dynamically disconnecting supply during inactive state. The 6T SRAM cell circuit using CNTFETs was simulated in HSPICE using Stanford CNFET model at 32nm technology node. The results shows that this method reduces leakage power by 31.5% compared with conventional 6T CNTFET SRAM Cell with minimal area overhead.

Keywords: SRAM Cell, CNTFET, Leakage Power, HSPICE.

# 1 Introduction

Rapid growth in semiconductor technology has lead to shrinking of feature sizes of transistors using nanometer process. This has allowed for very large circuits with complex functionality to be fabricated on a single chip. As transistor density keeps on increasing so does the power dissipated by the chip. Modern portable battery operated devices such as cellphones, laptops, PDAs are particularly affected by this as high power dissipation reduces battery service life. Thus, power dissipation has now become a vital design metric. Earlier, dynamic or switching power component dominated the total power dissipated by an IC. However, in nanometer regime static or leakage power becomes a dominant proportion of the total power dissipation [1]. Leakage power dissipation arises from the leakage currents flowing through the transistor when there are no input transitions and the transistor has reached steady

state. The most effective technique for reducing dynamic power dissipation is supply voltage scaling and to maintain performance, transistor threshold voltage also has to be scaled proportionally [2]. This has an adverse effect on leakage power. Thus, in the nanometer regime due to lower supply voltages, leakage power cannot be neglected. To curtail this static power loss, several techniques have been proposed that efficiently minimize leakage power dissipation [3-4].

Since the first CNTFET was reported in 1998, great progress has been made during the past years in all the areas of CNFET science and technology, including materials, devices, and circuits [5]. Carbon Nano Tubes (CNTs) are sheets of graphene rolled into tube. A CNTFET is the analogue of silicon MOSFET in which Single Wall CNTs (SWCNT) replace the silicon channel. Depending on their chirality (i.e., the direction in which the graphite sheet is rolled), the SWCNTs can either be metallic or semiconducting. CNFETs are one of the molecular devices that avoid most fundamental silicon transistor restriction and have ballistic or near ballistic transport in their channel. Therefore a semiconductor CNT is appropriate for using as channel of FETs. Applied voltage to the gate can control the electrical conductance of the CNT by changing electron density in the channel [6].

The SRAM leakage power has also become a more significant component of total chip power as a large portion of the total chip transistors directly comes from on-die SRAM. The dominant leakage power component is the subthreshold leakage. Effectively lowering power supply decreases all the leakage components. Since the activity factor of a large on-die SRAM is relatively low, it is much more effective to put in a power reduction mechanism dynamically, which modulates the power supply. But when the SRAMs are required to keep the data retention as the power supply is lowered, the rail-to-rail voltage needs to be carefully controlled to maintain sufficient cell stability, avoiding potential data loss. Especially for modern VLSI processor design, SRAM takes large part of power consumption portion and area overhead. While seeking for solutions with higher integration, performance, stability, and lower power, CNT has been presented for next-generation SRAM design as an alternative material in recent years [7-11]. Hence, this necessitates the need for techniques to reduce this leakage power dissipation in CNTFET based SRAM cell.

## 2 Leakage Paths in SRAM Cell

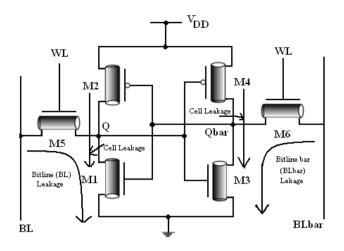

Leakage power dissipation arises from the leakage currents flowing through the transistor when there are no input transitions and the transistor has reached steady state. The leakage paths in conventional 6T CNTFET SRAM cell are shown in Fig.1. There are two dominant sub-threshold leakage paths in a 6T SRAM cell: one from  $V_{DD}$  to ground paths inside the SRAM cell, called Cell leakage paths and second from the bitlines 'BL' (or bit-bar line 'BLbar') to ground path through the pass transistor M5 (or M6), called Bitline leakage paths [12].

Fig. 1. Leakage paths in 6T CNTFET SRAM Cell

#### 3 Proposed SRAM Cell Design

Subthreshold leakage current and leakage energy dissipation increase exponentially with decreasing threshold voltage. To prevent leakage energy dissipation in a CNTFET SRAM Cell from limiting aggressive threshold-voltage scaling, this paper proposes a Sleep Transistor approach. This sleep transistor technique is applied to SRAM cell based on CNTFETs. Sleep Transistor enables a CNTFET SRAM Cell to "turn off" the supply voltage and eliminate virtually all the leakage energy dissipation in the SRAM's unused sections. The key idea is to introduce an extra transistor in the supply voltage ( $V_{DD}$ ) or the ground path (GND) of the CNTFET SRAM cells; the extra transistor is turned on in the used sections and turned off in the unused sections. Sleep approach maintains the performance advantages of lower supply and threshold voltages while reducing leakage and leakage energy dissipation. The fundamental reason for the reduction in leakage is the stacking effect of self reverse-biasing series-connected transistors. Extra transistor of the sleep transistor approach produces the stacking effect in conjunction with the CNTFET SRAM cell transistors when the sleep transistor is turned off.

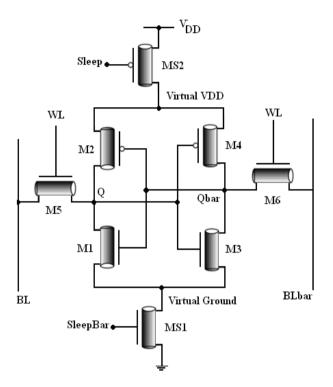

The proposed CNTFET SRAM cell with Sleep transistors is shown in Fig. 2. PMOS sleep transistor MS2 is connected between  $V_{DD}$  and the CNTFET SRAM PMOS transistors and NMOS sleep transistor MS1 is connected between GND and the CNTFET SRAM NMOS transistors. These Sleep transistors MS1 and MS2 are turned on for the cell to be in "active" mode and turned off for the cell to be in "standby" mode. These two sleep transistors MS1 and MS2 are controlled by a signal called 'Sleep'. This control signal is '1' in sleep mode and '0' in active mode, so that the sleep transistors are ON in active mode and OFF during inactive or standby mode. This CNTFET based SRAM cell is in active mode when the control signal 'WL' is '1' and is in inactive or sleep mode when 'WL' is '0'. When a control signal 'WL' is '0', a 'Sleep' is set to '1' and 'SleepBar' to '0' so that sleep transistors MS1 and MS2 are OFF, there by leakage currents are reduced and hence leakage power.

Fig. 2. 6T SRAM cell using CNTFETs with Sleep Transistor

These Sleep Transistors MS1 and MS2 can be shared among multiple SRAM cells to amortize the overhead. To reduce the impact on SRAM cell speed and to ensure stability of the SRAM, the sleep transistors must be carefully sized with respect to the SRAM cell transistors when they are gating. While these sleep transistors must be made large enough to sink the current flowing through the SRAM cells during a read/write operation in the active mode, too large a sleep transistor may reduce the stacking effect, thereby diminishing the energy savings. Moreover, large transistors also increase the area overhead.

#### 4 Results and Discussions

Synopsis HSPICE is used for simulation purpose to estimate delay and power consumption. Simulations performed with Stanford CNTFET model at 32nm feature size with supply voltage  $V_{DD}$  of 0.9V [13]. The HSPICE Cscope is used for

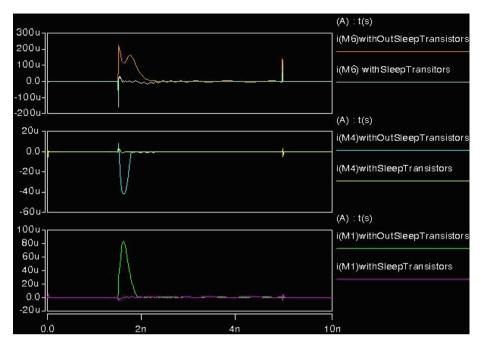

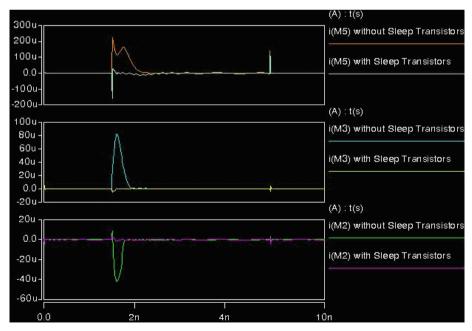

displaying simulation waveforms. Simulation waveforms of leakage currents through off transistors M1, M4 and M6 of a 6T CNTFET SRAM Cell for assumed storage bit of Q='1' without and with sleep transistors are shown in Fig. 3 and these leakage current values are tabulated in Table 1. Similarly simulation waveforms of leakage currents through off transistors M2, M3 and M5 of a 6T CNTFET SRAM Cell for assumed storage bit of Q='0' without and with sleep transistors are shown in Fig. 4 and these leakage current values are tabulated in Table 2. From these waveforms it is conformed that the leakage currents through off transistors of 6T CNTFET SRAM Cell with Sleep Transistors are very small compared to 6T CNTFET SRAM cell with out Sleep Transistors. This technique is reducing the leakage power in 6T CNTFET SRAM cell without sleep transistor with the same delay but at the cost of minimal increase of area. Simulated results of CNTFET SRAM cell with and without Sleep Transistors are and summarized in Table 3 for comparison.

| Sl. | Leakage Currents | 6T CNTFET SRAM Cell       | 6T CNTFET SRAM Cell    |

|-----|------------------|---------------------------|------------------------|

| No. | (A)              | Without Sleep Transistors | With Sleep Transistors |

| 1   | I (M1)           | 1.767e-06                 | 1.130e-08              |

| 2   | I(M4)            | 7.133e-07                 | 2.365e-08              |

| 3   | I(M6)            | 6.789e-06                 | 3.168e-07              |

| 4   | Total Leakage    | 7.843e-06                 | 3.292e-07              |

| S1. | Leakage Currents | 6T CNTFET SRAM Cell       | 6T CNTFET SRAM Cell    |

|-----|------------------|---------------------------|------------------------|

| No. | (A)              | Without Sleep Transistors | With Sleep Transistors |

| 1   | I (M2)           | 1.767e-06                 | 1.117e-08              |

| 2   | I(M3)            | 7.133e-07                 | 2.350e-08              |

| 3   | I(M5)            | 6.829e-06                 | 2.758e-07              |

| 4   | Total Leakage    | 7.883e-06                 | 2.882e-07              |

| Table 3 | <b>3.</b> Sir | nulation | Results |

|---------|---------------|----------|---------|

|---------|---------------|----------|---------|

| S1. | Parameter      | 6T CNTFET SRAM Cell 6T CNTFET SRAM Cel |                        |

|-----|----------------|----------------------------------------|------------------------|

| No. |                | Without Sleep Transistors              | With Sleep Transistors |

| 1   | Leakage Power  | 6.95E-9                                | 4.76E-9                |

|     | (W)            |                                        |                        |

| 2   | Read Delay (S) | 2.401E-10                              | 2.399E-10              |

|     |                |                                        |                        |

| 3   | SNM (mV)       | 154                                    | 109                    |

|     |                |                                        |                        |

**Fig. 3.** Leakage currents flowing through the 6T CNTFET SRAM cell with and without Sleep Transistors when Q='1'

**Fig. 4.** Leakage currents flowing through the 6T CNTFET SRAM cell with and without Sleep Transistors when Q='0'

# 5 Conclusion

CMOS technology in nanometer scale faces great challenge due to sub-threshold leakage power Consumption. In this paper a conventional 6T SRAM cell based on CNTFET is designed for leakage power reduction by applying Sleeping Transistors technique. The results show that this design reduces a leakage power to the significant effect by maintaining delay but with minimal increase in area. Proposed cell can be used in design of CNTFET based ultra-low SRAM Memories. This cell can be used for design of low-leakage memory based on CNTFET technology.

### References

- 1. International Technology Roadmap for Semiconductors by Semiconductor Industry Association (2009), http://public.itrs.net

- Mutoh, S., Douseki, T., Matsuya, Y., Aoki, T., Shigematsu, S., Yamada, J.: 1-V power supply high-speed digital circuit technology with multi threshold-voltage CMOS. IEEE J. Solid-State Circuits 30(8), 847–854 (1995)

- Powell, M., Yang, S.H., Falsafi, B., Roy, K., Vijaykumar, T.N.: Gated-V<sub>DD</sub>: A Circuit Technique to Reduce Leakage in Deep-submicron Cache Memories. In: International Symposium on Low Power Electronics and Design, pp. 90–95 (2000)

- 4. Kim, K.K., Nan, H., Choi, K.: Power Gating for Ultra-Low Voltage Nanometer ICs. In: IEEE ISCAS (2010)

- Patil, N., Lin, A., Zhang, J., Wong, H.S.P., Mitra, S.: Digital VLSI logic technology using Carbon Nanotube FETs: Frequently Asked Questions. In: 46th ACM-IEEE Design Automation Conference, pp. 304–309 (2009)

- Appenzeller, J.: Carbon Nanotubes for High-Performance Electronics—Progress and Prospect. Proc. IEEE 96(2), 201–211 (2008)

- Yu, Z., Chen, Y., Nan, H., Wang, W., Choi, K.: Design of Novel Low Power 6T CNFET SRAM Cell Working in Sub-Threshold Region. In: IEEE International Conference on Electro/Information Technology (2011)

- Wang, W., Choi, K.: Novel curve fitting design method for carbon nanotube SRAM cell optimization. In: IEEE International Conference on Electro/Information Technology, EIT (2010)

- Kuresh, A.K., Hasan, M.: Performance comparison of CNFET- and CMOS-based 6T SRAM cell in deep submicron. Microelectronics Journal Archive 40(6), 979–982 (2009)

- Lin, S., Kim, Y.-B., Lombardi, F.: A New SRAM Cell Design Using CNTFETs. In: International SoC Design Conference, vol. 1, pp. 168–171 (2008)

- Lin, S., Kim, Y.B., Lombardi, F.: Design of a CNTFET-based SRAM cell by dualchirality selection. IEEE Transactions on Nanotechnology 9(1), 30–37 (2010)

- Kim, C., Roy, K.: Dynamic V<sub>t</sub>SRAM: A Leakage Tolerant Cache Memory for Low Voltage Microprocessors. In: Proceedings of the International Symposium on Low Power Electronics and Design, USA, pp. 251–254 (2002)

- Stanford University CNFET Model website, http://nano.stanford.edu/model.php?id=23