# **Realization of SDR in Partial Reconfigurable FPGA Using Different Types of Modulation Techniques**

Neenu Joseph and P. Nirmal Kumar

Department of ECE, Anna University, Chennai neenuj@gmail.com, nirmal@annauniv.edu

Abstract. The increase in the consumer demand and the exponential growth for wireless systems, which enables consumer to communicate in any place by means of information, has in turn led to the emergence of many portable wireless communication products. The present research works primarily targets to integrate as much as signal processing applications in a single portable device. Since integration through software applications compromises system speed, integration through hardware will be the better compliment. Software Defined Radio (SDR) Technology yields to achieve this small form factor system while keeping power consumption under the limit. SDR enables soft changeable system functionality, such as receiver demodulation technique. The flexibility of changing the receiver functionality in runtime is usually attained by FPGA. However, using a complete FPGA for reconfiguration of a particular functionality is not an efficient method in terms of power consumption and switching time. We proposed a SDR architecture using a recent advancement in FPGAs, called Partial Reconfiguration (PR). PR helps to change certain portion of FPGA, while the rest keeps functioning. It also reduces the total hardware usage and hence the power. The different demodulation technique and other signal processing application from an external memory unit can be loaded into FPGA PR modules while the other parts of FPGA doing a constant data processing.

**Keywords:** Partial Reconfiguration in FPGA, Modulation Techniques, Wireless communication.

# 1 Introduction

SDR is a collection of Hardware and software in which all the radio functions can be implemented using software coding or firmware on a processing system. These software can be alterable according to the applications in communication system. The processing systems include Field Programmable Gate Arrays (FPGA), Digital Signal Processors (DSP), General Purpose Processors (GPP), Programmable System on Chip (SoC) or other Application Specific Programmable Processors. The use of SDR technologies allows new wireless features like Third Generation (3G) and Fourth Generation (4G) capabilities to be added to existing Generation for mobile applications and radio systems without requiring new hardware.

<sup>©</sup> Institute for Computer Sciences, Social Informatics and Telecommunications Engineering 2012

By using SDR Technique a family of Radio products used in communication to be developed in common platform architecture and lot of research work is going on in this area allowing new products will come quickly into market. Since the software to be reused across radio products, the development cost reduces dramatically. This type of wireless communication enables the user to communicate with whomever they need to communicate and in whatever manner according to their wish. For example video call is available in Third generation. Likewise any type of applications can be include using SDR in a single chip. The main advantage SDR engineers is to provide a single radio transceiver capable of playing the roles of cordless telephone, cell phone(GSM and CDMA), wireless fax, wireless e-mail system, pager, wireless videoconferencing unit, wireless Web browser, Global Positioning System unit, and other functions still in the realm of science fiction, operable from any location on the surface of the earth, and perhaps in space as well.

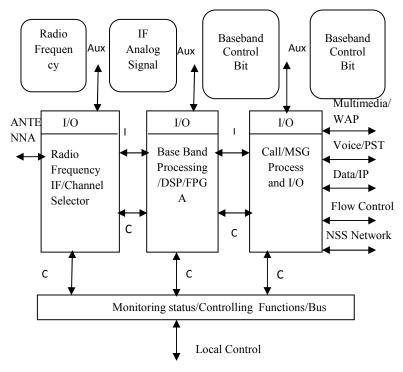

The General block diagram of SDR is shown in Figure 1. The radio frequency signal comes from antenna is down converted to baseband frequency range with the help of transceivers. The analog to digital converter will give the digital data to the processing module. The processing module will be a combination of FPGA and DSP in most cases. FPGA will be reconfigured by DSP according to the incoming signals modulation scheme or depends on the user's interest. Finally the original message signal will be given to a respected sink device.

The SDR is software radio in which all the physical layers are software defined. It effectively uses the area in FPGA.

Fig. 1. Basic Diagram of SDR

# 2 General Implementation

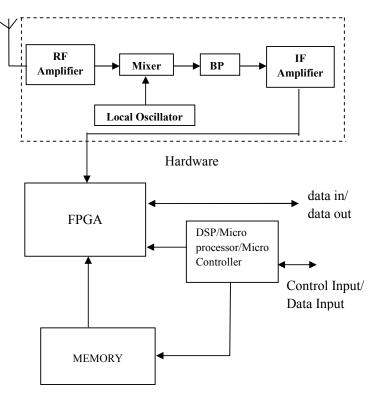

The generalized implementation (block diagram) method of SDR system architecture is shown in figure 2. All software part is done in FPGA. This can be alter according to the applications.

The FPGA shown here is used for the soft reconfiguration and the DSP or any GPPs will do controlling of the FPGA and other data flow tasks. The combination of devices like DSP,FPGA, GPP is used in SDR, due to the advantage and disadvantage of each device.

DSP - good for software processing, branches but lack in parallelism.

FPGA- gives parallel architecture, high data rates but issues with software routine executions.

GPP- good for managing and controlling memories and peripherals but not optimized for algorithms development.

In most cases DSP is used because the combination of controlling ability and signal processing power. The different demodulation techniques configuration will be loaded into a memory unit initially. The choice will be given to user to select the required demodulation technique. Once the DSP receives the command to change the receiver demodulation, it reconfigures the FPGA by loading corresponding bit stream

Fig. 2. General Implementation

from memory. Typical FPGA reconfiguration time will be in the order of 100s of milliseconds and this is huge delay when come into real time. Further this delay will increase if DSP running some other default communication task in parallel.

# 3 Proposed System Architecture

Due to the Rapid development in FPGAs, now we have all the following resources in single FPGA.

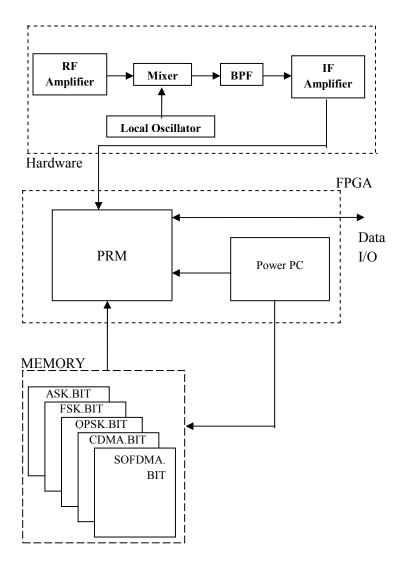

Fig. 3. Proposed system Architecture

#### Huge amount of Logic blocks: For more parallel logic designs.

DSP Slices: For signal processing algorithm implementation.

**PowerPC:** Embedded processor can be used as GPP. All these units can operate in parallel.

As shown in the block diagram, we have proposed a SDR architecture with only FPGA due to the availability of massive parallelism and Partial Reconfigurable ability. Since the newer FPGA provides PR modules, it is possible to change of the certain part of FPGA alone and hence we can avoid complete FPGA for reconfiguration. The embedded PowerPC and DSP slices can do a work of a GPP or DSP. Hence it is also not required to use dedicated ASIC for the controlling and signal processing purpose. The proposed architecture embeds everything into a single FPGA which in turn reduces the total resource utilization and hence the power and speed.

Our design mainly concentrates on runtime reconfiguration of demodulation techniques in Partial Reconfiguration blocks of an FPGA and keeping the rest of the baseband process unchanged. The modulation/demodulation techniques will be ASK, FSK, BPSK QPSK SOFDMA and CDMA.

### 4 Partial Reconfiguration

Xilinx introduced this method of reconfiguration to the market recently. As "Field Programmable Gate Array" name suggests, it gives user the flexibility to reconfigure the hardware on field instead of going through the complete ASIC design process for small modification or updation in the design. The new Partial Reconfiguration capability of recent FPGAs further enhances the flexibility by allowing partial configuration on an operating FPGA using partial bit files.

After a full bit file configures the FPGA, partial bit files can be downloaded to modify reconfigurable regions in the FPGA without compromising the integrity of the applications running on those parts of the device that are not being reconfigured.

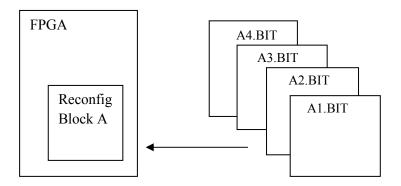

As shown in Figure 4, the function implemented in Reconfigurable Block A is modified by downloading one of several partial bit files, A1.bit, A2.bit, A3.bit or

Fig. 4. Partial Reconfiguration in FPGA

A4.bit. The logic in the FPGA design is divided into two different categories, reconfigurable logic and static logic. The reconfigurable block A represents reconfigurable logic and the rest are static logic. The static logic remains functioning and is completely unaffected by the loading of a partial bit file. The reconfigurable logic is replaced by the contents of the partial bit file. There will be a Configuration controller which is part of the static module. This takes care of loading and unloading of dynamic modules. The command to this controller will be given from PowerPC with the reconfiguration data.

# 5 Conclusion

Realization of SDR in Partial Reconfigurable FPGA using different types of Modulation Techniques Developing using Xilinx FPGA. Due to the Realization is done by using the help of Partial Reconfiguration. The Speed and performance can be improved. The area also can be decreased. The New Xilinx, Vertex Series FPGA provides the provision of Partial Reconfiguration. The power Consumption can be reduced by applying power reduction Techniques in the blocks. In future, more types of modulation techniques can be done in same chip using Partial Reconfiguration with high performance.

This Receiver can be used in Mobile stations, Radio Stations etc. The use of Partial reconfiguration any function can alter at any time without affecting the current operation. The demodulation Techniques in the receiver side is stored in partial Reconfigurable blocks. The physical layers of SDR implemented in the FPGA.

### 6 Result

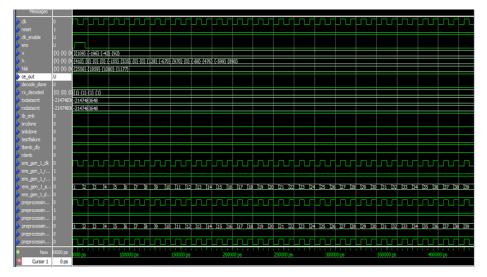

The Simulation is done by using Modelsim 6.4a. The Synthesis is done by using Xilinx ISE Software. The Simulation results are shown in the figure 5 and figure 6.

| 😦 wave - default                                                   |              |           |         |      |     |      |      |            |       |            |      |            |

|--------------------------------------------------------------------|--------------|-----------|---------|------|-----|------|------|------------|-------|------------|------|------------|

| Messages                                                           |              |           |         |      |     |      |      |            |       |            |      |            |

| 🖃 🔷 /inputsampling/sam                                             | 110011011011 | 110011    | 111011  |      |     |      | 1    | 100110     | 01011 |            |      |            |

| (11)                                                               | 1            |           |         |      |     |      |      |            |       |            |      |            |

| (10)                                                               | 1            |           |         |      |     |      |      |            |       |            |      |            |

|                                                                    | 0            |           |         |      |     |      |      |            |       |            |      |            |

|                                                                    | 0            |           |         |      |     |      |      |            |       |            |      |            |

|                                                                    | 1            |           |         |      |     |      |      |            |       |            |      |            |

|                                                                    | 1            |           |         |      |     |      |      |            |       |            |      |            |

| <u>&gt;</u> (5)                                                    | 0            |           |         |      |     |      |      |            |       |            |      |            |

| (4)<br>(3)                                                         | 1            |           |         |      |     |      |      |            |       |            |      |            |

|                                                                    | 1            |           |         |      |     |      |      |            |       |            |      |            |

|                                                                    | 1            |           |         |      |     |      |      |            |       |            |      |            |

|                                                                    | 1            |           |         |      |     |      |      |            |       |            |      |            |

| (0) /inputsampling/clk                                             | <u>.</u>     |           |         | Ь    | _   |      | , F  |            |       |            |      |            |

| <ul> <li>/inputsampling/cik</li> <li>/inputsampling/rdy</li> </ul> | 1            |           |         |      |     |      |      |            |       |            |      |            |

| /inputsampling/idy                                                 | 110011011011 | 11001     | 1111011 |      |     |      | _    |            |       | X1100      | 1100 | 1011       |

| +                                                                  | 3            | <u>У1</u> | 12 13   | io i | 1   | 2 13 | - 10 | Ϋ́1        | 12    | 13         | 100  | Y1 Y       |

|                                                                    | 3            |           |         | r    | =   | 2 13 | -6   | <u></u>    | 12    | 13         | 6    | - <u>}</u> |

| +                                                                  | 110011011011 | 110011    | 1111011 |      |     | ~ ~  |      | <u>∿</u> ± | -     | χ<br>11100 |      | 1011       |

|                                                                    |              |           |         |      |     |      |      |            |       |            |      |            |

|                                                                    |              |           |         |      |     |      |      |            |       |            |      |            |

|                                                                    |              |           |         |      |     |      |      |            |       |            |      |            |

|                                                                    |              |           |         |      |     |      |      |            |       |            |      |            |

|                                                                    |              |           |         |      |     |      |      |            |       |            |      |            |

| -<br>≏≣⊛ Now                                                       | 630.2 ns     | 9.5 ns    |         |      | 620 |      | • •  | 1 1 1      |       | 0.5 ns     |      | 1.1.1      |

| 🚔 🖉 😑 Cursor 3                                                     | 626.967 ns   |           |         |      |     |      |      |            |       |            |      |            |

Fig. 5. Input Sampling in SDR

Fig. 6. Simulation Result

## References

- [1] Bhargav Alluri, V., Robert Health, J., Lhamon, M.: A new Multichannel, coherent Amplitude Modulated, time Division Multiplexed. Software Defined Radio Architecture and Field Programmable Gate Array

- [2] Partial Reconfiguration of Virtex FPGAs in ISE 12:- Xilinx

- [3] Glossner, J., Inacu, D., Lu, J., Hokenek, E., Moudgill, M.: A Software Defined Communications baseband design. IEEE Communication Mag. 41(1), 120–128 (2003)

- [4] Zhigang, L., Wei, L., Yan, Z., Wei, G.: Multi standard SDR base band platform. In: Proc. IEEE Int. Conf. Computer Networks and Mobile Computing, pp. 461–464 (2003)

- [5] Yoshida, H., Tsurumi, H., Suzuki, Y.: Broadband RF front-end and software execution procedure in software defined radio. In: Proc. IEEE Veh. Technol. Conference, vol. 4, pp. 2133–2137 (1999)

- [6] Rivet, F., Deval, Y., Begueret, J.B., Dallet, D., Belot, D.: A disruptive software-defined radio receiver architecture based on sampled analog signal processing. In: Proc. IEEE Radio Frequency Integr. Circuits (RFIC) Symp., June 3-5, pp. 197–200 (2007)

- [7] Abidi, A.A.: The path to the software-defined radio receiver. IEEE J. Solid-State Circ. 42(5), 954–966 (2007)

- [8] FPGA Run-Time Reconfiguration: Two Approaches, http://www.Altera.com

- [9] A software Defined Radio for the masses, part1: Gerald Youngblood, AC5OG

- [10] A software Defined Radio for the masses, part2: Gerald Youngblood, AC5OG

- [11] Partial Reconfiguration User Guide:- Xilinx

- [12] Mitola, J.: The software radio architecture. IEEE Commun. Mag. 33(5), 26–38 (1995)

- [13] SDR IEEE P1900 Standard, http://standards.ieee.org